# UNIVERSIDAD AUTONOMA DE QUERETARO FACULTAD DE INGENIERÍA INGENIERÍA EN AUTOMATIZACIÓN

Sistema Generador de Vibraciones

## **TESIS**

Que como parte de los requisitos para obtener el título de Ingeniero en Automatización con línea terminal en Mecatrónica

Presenta:

Julio César Vargas Cano

Dirigido por:

Dr. José Marcelino Gutiérrez Villalobos

# Dirección General de Bibliotecas y Servicios Digitales de Información

Sistema Generador de Vibraciones

## por

Julio César Vargas Cano

se distribuye bajo una Licencia Creative Commons Atribución-NoComercial-SinDerivadas 4.0 Internacional.

**Clave RI:** IGLIN-233523

## Sistema Generador de Vibraciones

Julio César Vargas Cano

#### RESUMEN

El análisis sísmico de estructuras civiles tiene gran importancia en el diseño y la construcción gracias al avance tecnológico desarrollado a través de los años. Los nuevos sistemas de pruebas sísmicas permiten realizar ensayos dinámicos de las estructuras realizando movimientos controlados de posición y realizando pruebas con frecuencias y amplitudes específicas. El objetivo del presente trabajo es el diseño de un sistema capaz de controlar la posición de un motor de corriente directa sin escobillas (BLDC) con base en tecnología Field Programmable Gates Array (FPGA), el cual, mediante una transformación mecánica de movimiento rotacional en lineal, opera el movimiento de una plataforma con distintos modos de operación entre los que destaca la capacidad de generar señales de posición senoidales a diferentes frecuencias y amplitudes. Todo el sistema se controla por una interfaz gráfica donde el usuario puede preestablecer el movimiento senoidal además de observar la posición de la plataforma y los valores arrojados por los distintos acelerómetros.

**Palabras** Clave: Control de posición, motor BLDC, FPGA, señal senoidal, frecuencia y amplitud.

#### **ABSTRACT**

The seismic analysis of civil structures has taken a lot of importance thought the pass of years thanks to technology develop in construction and design. The new systems for seismic proofs allow make dynamic tests in structures making controlled movements of position and try with established frequency and amplitude values. The objective of this work is design a system capable of control the position of a brushless direct current motor (BLDC) based on Field Programmable Gates Array (FPGA) technology; which, through a mechanical transformation for rotational movement into lineal movement, manipulate the movement of a platform with some operation modes. One of those modes are the sinusoidal mode which is capable to generate sinusoidal position signals in different frequencies and amplitudes. All the system will be controlled by a Human-Machine Interface where the user could pre-establish the values of the sinusoidal movement besides could observe the actual position of the platform and the values acquired by the accelerometers in the structure.

**Keywords**: Position control, BLDC Motor, FPGA, sinusoidal signal, frequency and amplitude.

## **AGRADECIMIENTOS**

A mis padres Rafaela y Julio que trabajaron mucho por lograr que yo alcanzara mis sueños, siempre me apoyaron y dieron lo mejor de sí por mí bienestar. Su cariño siempre me motivó a continuar trabajando y nunca detenerme.

A mis hermanos que con su gran apoyo y fuerza me guiaron y me empujaron a terminar, me enseñaron a jamás darme por vencido y a enfrentar los retos que la vida me ha puesto. Los quiero mucho.

A mis amigos y profesores que siempre me inspiraron y me demostraron que soy capaz de alcanzar grandes metas.

## ÍNDICE DE CONTENIDO

| RESUM  | MEN                           | I   |

|--------|-------------------------------|-----|

| ABSTR  | RACT                          | II  |

| AGRAI  | DECIMIENTOS                   | III |

| ÍNDICI | E DE CONTENIDO                | IV  |

| ÍNDICI | E DE TABLAS                   | VI  |

| INDICE | E DE FIGURAS                  | VI  |

| CAPÍT  | ULO 1:INTRODUCCIÓN            | 1   |

| 1.1    | Justificación                 | 3   |

| 1.2    | Planteamiento del problema    | 3   |

| 1.3    | Hipótesis y objetivos         | 4   |

| 1.3.   | .1 Hipótesis general          | 4   |

| 1.3.   | .2 Objetivo general           | 5   |

| 1.3.   | .3 Objetivos específicos      | 5   |

|        | ULO 2: REVISIÓN DE LITERATURA |     |

|        | Antecedentes                  |     |

| 2.1.   | _                             |     |

| 2.1.   | .2 Antecedentes generales     | 7   |

|        | TULO 3: METODOLOGÍA           |     |

| 3.1    | Marco teórico                 |     |

| 3.1.   |                               |     |

| 3.1.   | .2 El amplificador            | 12  |

| 3.1.3  | Encoder17                                  |

|--------|--------------------------------------------|

| 3.1.4  | Dispositivo mecánico19                     |

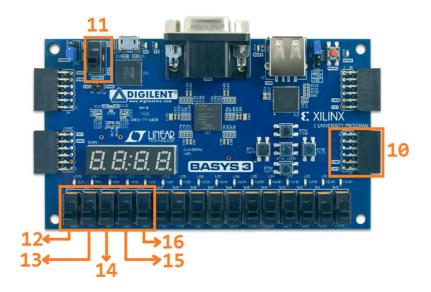

| 3.1.5  | Unidad de control20                        |

| 3.2 D  | Descripción de hardware FPGA23             |

| 3.2.1  | Protocolo I <sup>2</sup> C                 |

| 3.2.2  | Protocolo UART28                           |

| 3.2.3  | Cuadratura del encoder31                   |

| 3.2.4  | Controlador33                              |

| 3.2.5  | Saturador36                                |

| 3.3 I  | nterfaz gráfica37                          |

|        | LO 4:RESULTADOS Y DISCUSIÓN40 Resultados40 |

| 4.2    | Conclusiones67                             |

| BIBLOG | RAFÍA69                                    |

| ANEXOS | 71                                         |

| A1 Mar | nual de Usuario71                          |

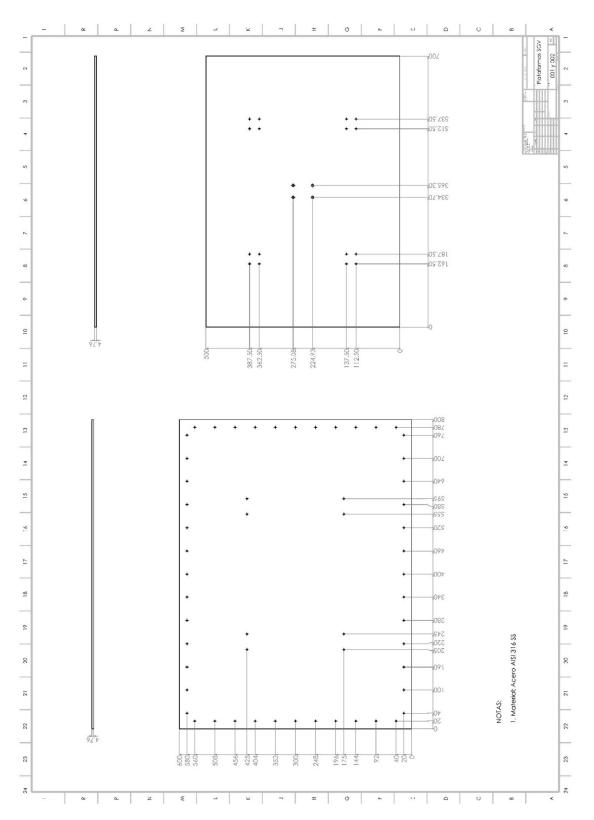

| A2 Mod | lelo CAD75                                 |

| A3 Cód | igo implementado en el FPGA77              |

## ÍNDICE DE TABLAS

| Tabla 1. Comportamiento de los voltajes a la salida del circuito10                          | 6 |

|---------------------------------------------------------------------------------------------|---|

| Tabla 2. Listado de componentes                                                             | 1 |

| Tabla 3. Valores para Kp54                                                                  | 4 |

| Tabla 4. Valor binario recibido para la Configuración y que significa5                      | 8 |

|                                                                                             |   |

| INDICE DE FIGURAS                                                                           |   |

|                                                                                             |   |

| Figura 1. Mesa vibratoria a cargo de la Coordinación de Estructuras y Materiales de la UNAM |   |

| Figura 2. Mesa vibratoria comercial Qanser, capacidad 7.5kg.                                |   |

| Figura 3. Diagrama interno de un motor BLDC1                                                | 0 |

| Figura 4. Partes del motor BLDC.                                                            | 1 |

| Figura 5. Comportamiento de las fases de un motor BLDC                                      | 1 |

| Figura 6. Arreglo interno para la conmutación de las fases12                                | 2 |

| Figura 7. Diagrama interno del DAC0800                                                      | 3 |

| Figura 8. Diagrama de bloques de un DAC I <sup>2</sup> C1                                   | 4 |

| Figura 9. Circuito OpAmp restador                                                           | 5 |

| Figura 10. Circuito de acoplamiento DAC-Amplificador10                                      | 6 |

| Figura 11. Comparación de encoder incremental y absoluto                                    | 7 |

| Figura 12. Secuencia del encoder.                                                           | 8 |

| Figura 13. Interior del bloque de deslizamiento.                                            | 0 |

| Figura 14. Diagrama a bloques del sistema de control de un cañón antiaéreo2                 | 1 |

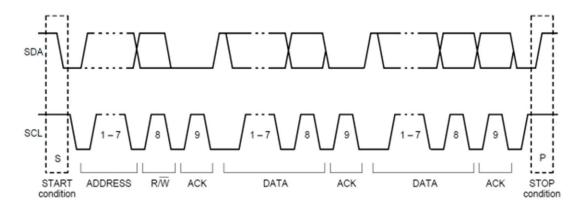

| Figura 15. Trama básica del protocolo I <sup>2</sup> C2                                     | 3 |

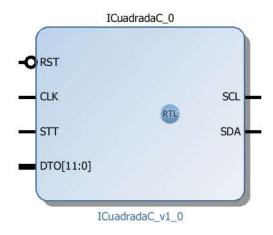

| Figura 16. Bloque del protocolo I <sup>2</sup> C                                            | 4 |

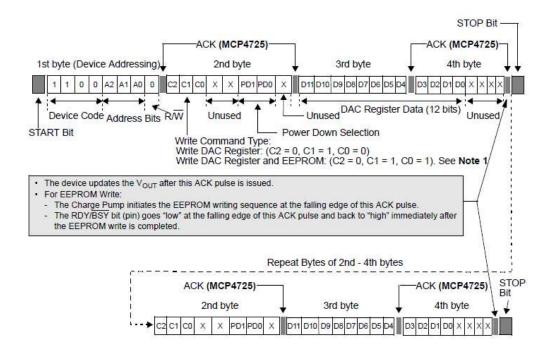

| Figura 17. Trama del protocolo para el circuito MCP4725                                     | 5 |

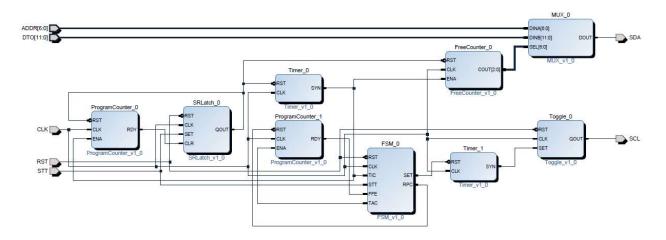

| Figura 18. Diagrama a bloques del protocolo I <sup>2</sup> C                                | 6 |

| Figura 19. Trama del MPU-6050                                                               | 6 |

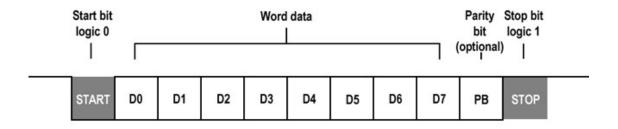

| Figura 20. Trama del protocolo UART.                                                        | 9 |

| Figura 21. Recepción de datos29                                                             | 9 |

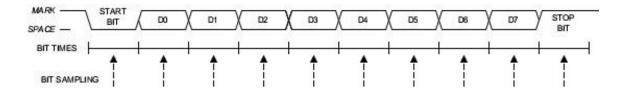

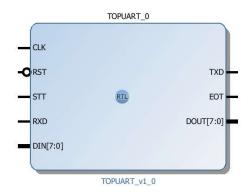

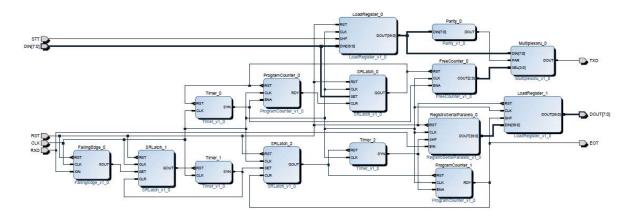

| Figura 22. Bloque UART.                                                                     | 30   |

|---------------------------------------------------------------------------------------------|------|

| Figura 23. Composición del protocolo UART                                                   | 30   |

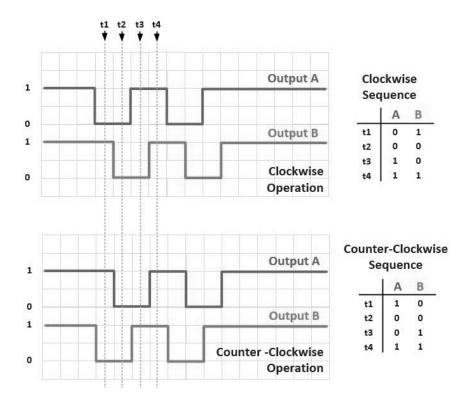

| Figura 24. Secuencia del encoder                                                            | 32   |

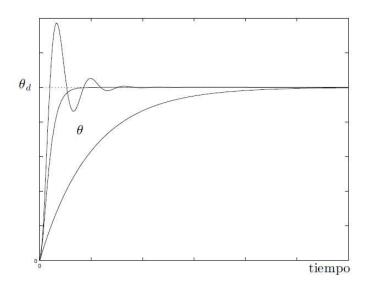

| Figura 25. Formas de la posible respuesta transitoria de un control de posición             | 33   |

| Figura 26. Diagrama a bloques del controlador PD                                            | 36   |

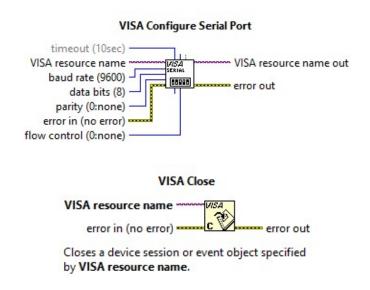

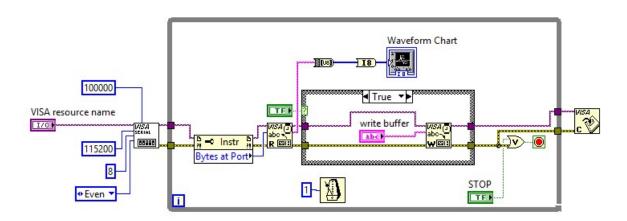

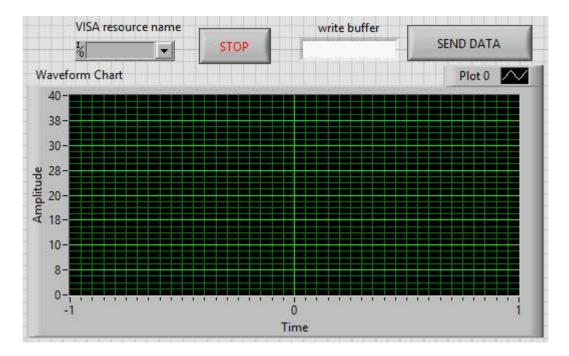

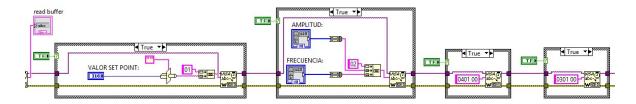

| Figura 27. Bloque de configuración Serial y bloque de fin de comunicación                   | 37   |

| Figura 28. Bloques de la lectura y escritura                                                | 38   |

| Figura 29. Programa a bloques de una interfaz de comunicación                               | 38   |

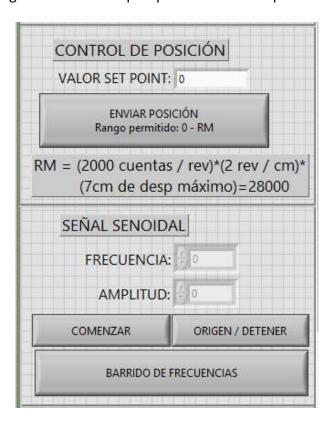

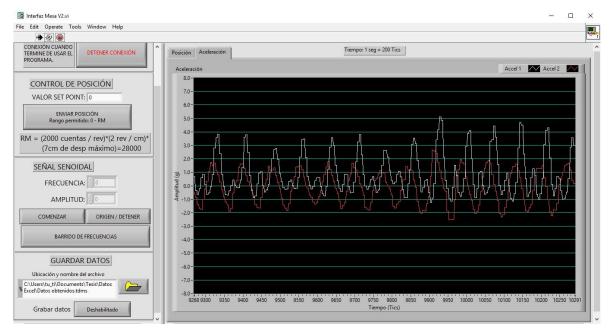

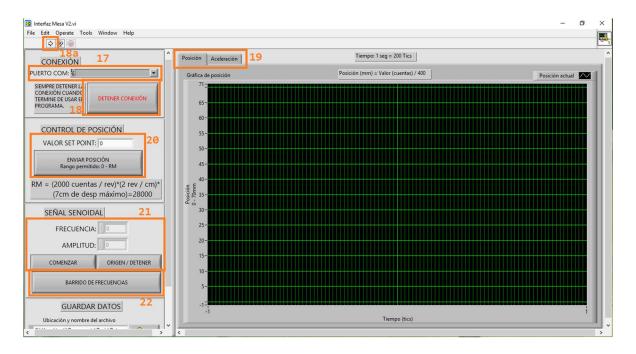

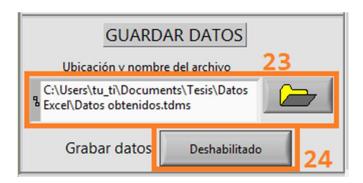

| Figura 30. Interfaz gráfica del programa desarrollado                                       |      |

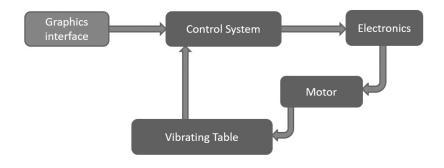

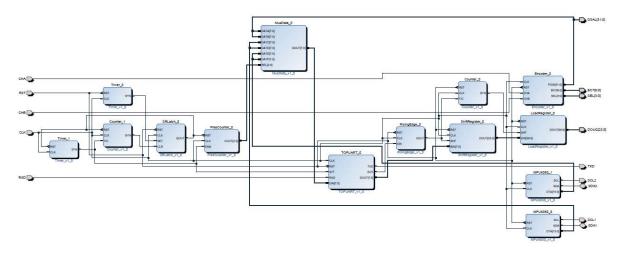

| Figura 31. Diagrama a bloques del sistema generador de vibraciones                          | 41   |

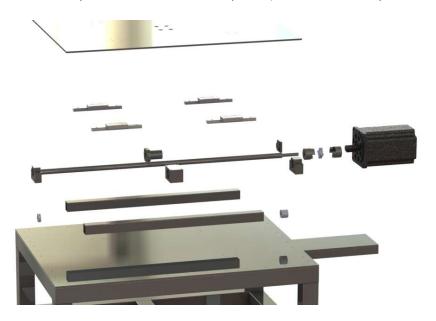

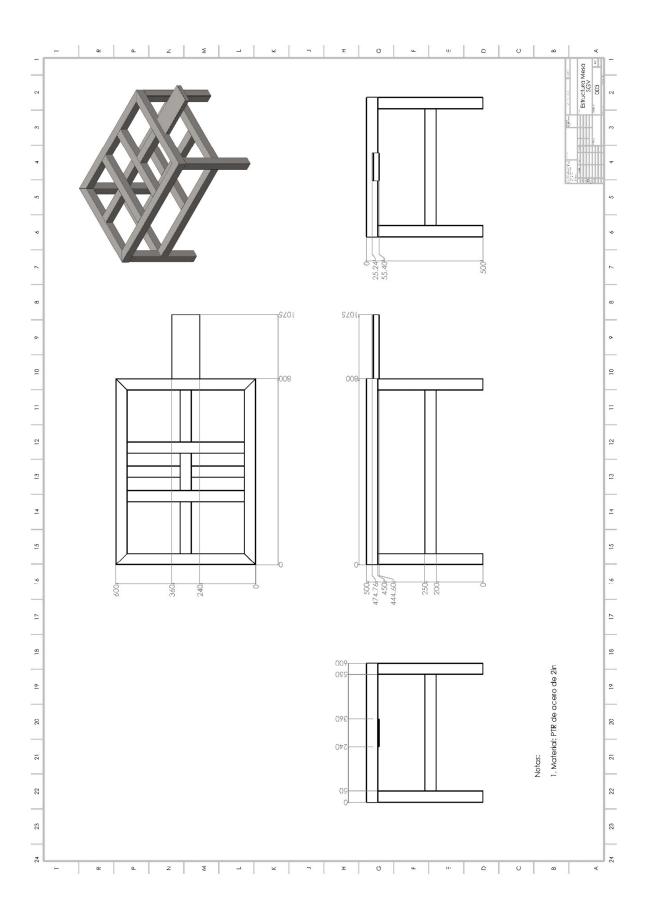

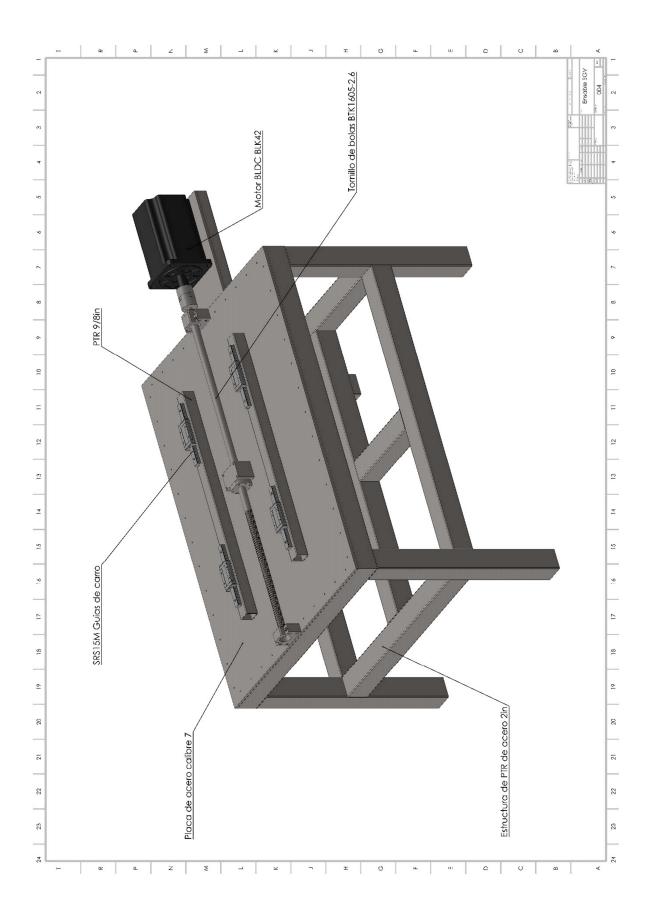

| Figura 32. Diseño conceptual prototipo de la mesa vibratoria                                | 42   |

| Figura 33. Vista superior del diseño conceptual (Vista de los componentes)                  | 43   |

| Figura 34. Vista explosionada de los componentes                                            | 43   |

| Figura 35. Vista general de la estructura del prototipo                                     | 44   |

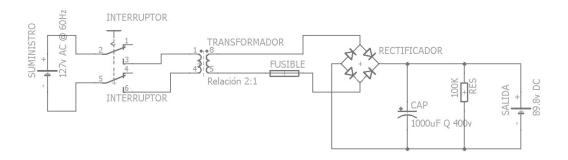

| Figura 36. Circuito de potencia que suministra energía al Servo Drive                       | 45   |

| Figura 37. Componentes del bloque ICuadradaC                                                | 46   |

| Figura 38. Componentes del bloque Encoder                                                   | 46   |

| Figura 39.Vista general del circuito electrónico                                            | 47   |

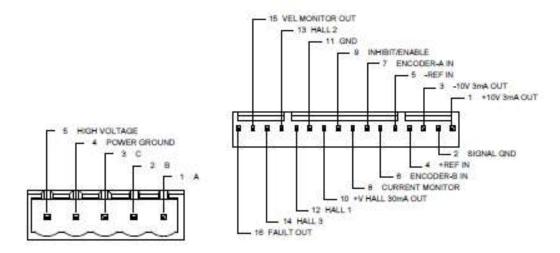

| Figura 40. Conexiones en el Servo Drive                                                     | 48   |

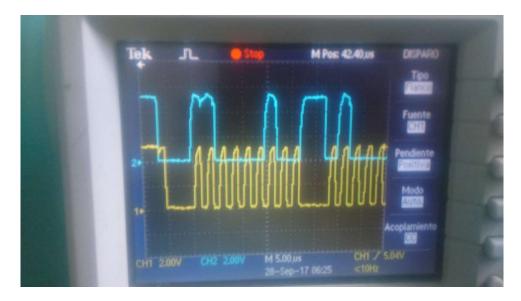

| Figura 41. Señal de control mediante el protocolo I <sup>2</sup> C                          | 48   |

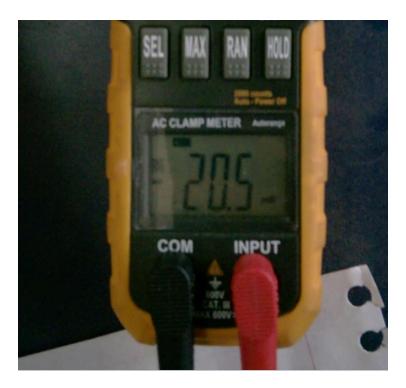

| Figura 42. Valor de voltaje con el motor detenido                                           | 49   |

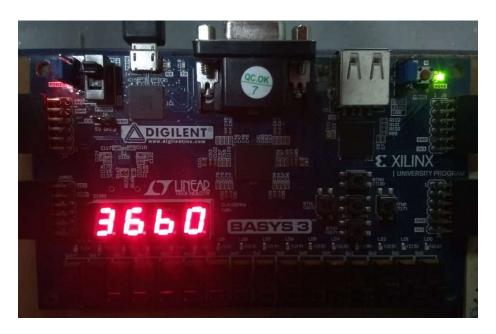

| Figura 43. Visualización del valor del encoder en el FPGA                                   | 50   |

| Figura 44. Implementación para enviar y recibir datos                                       | 51   |

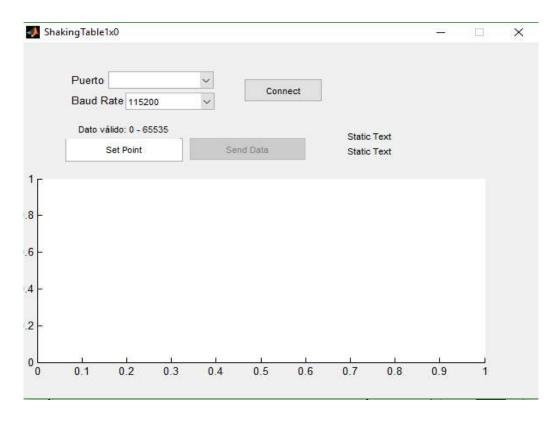

| Figura 45. Interfaz gráfica en Matlab                                                       | 52   |

| Figura 46. Código implementado en el bloque de Saturador                                    | 53   |

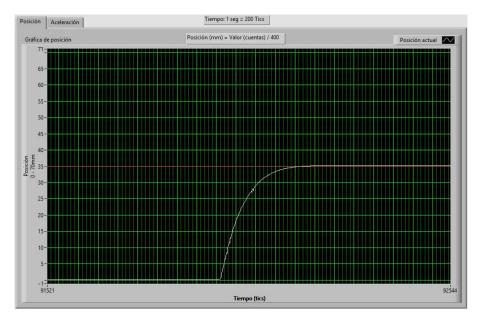

| Figura 47. Respuesta del controlador con Kp=1                                               | 54   |

| Figura 48. Código implementado en el bloque Saturador con diferente valor de Kp             | . 55 |

| Figura 49. Respuesta al escalón con Kp=0.25.                                                | 55   |

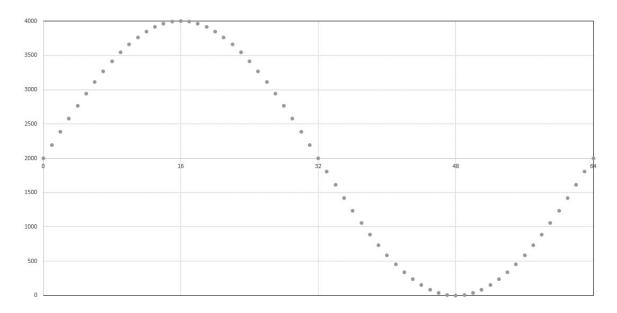

| Figura 50. Discretización de la señal senoidal en 64 puntos para crear la Señal<br>Unitaria | 56   |

| Figura 51. Diagrama de bloques de la posición deseada tipo senoidal                         | 57   |

| Figura 52. Código implementado del MuxPosición                                              | 58   |

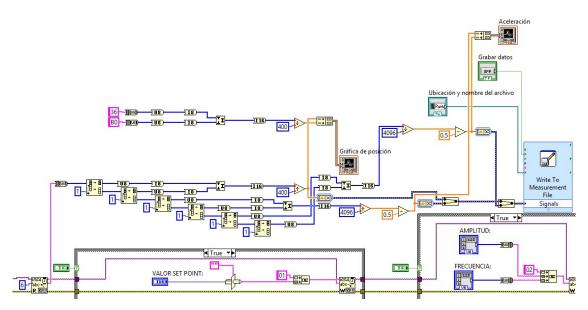

| Figura 53. Programación en bloques para enviar datos para múltiples tareas                  | 59   |

| Figura 54. Parte de la interfaz que controla los Modos de operación   | 59 |

|-----------------------------------------------------------------------|----|

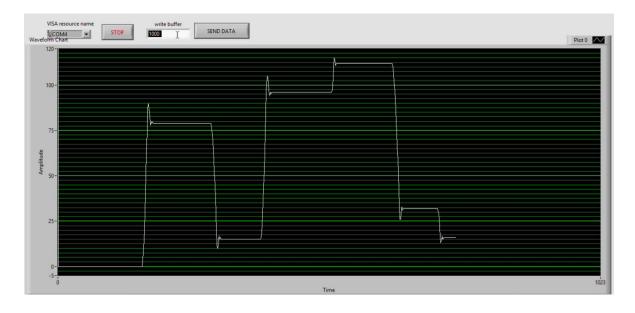

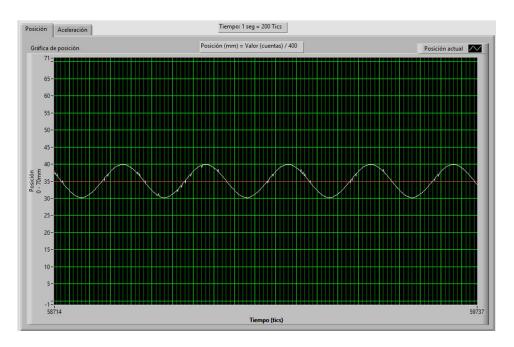

| Figura 55. Funcionamiento de la respuesta senoidal con Frec=1 y Amp=1 | 60 |

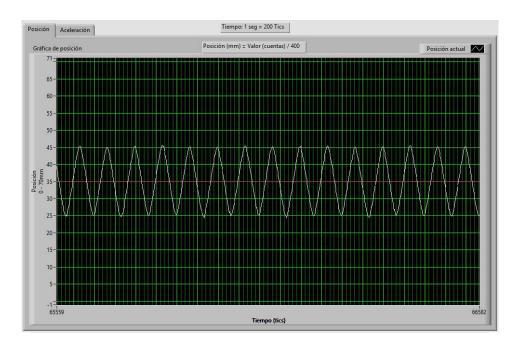

| Figura 56. Respuesta senoidal con Frec=3 y Amp=5                      | 61 |

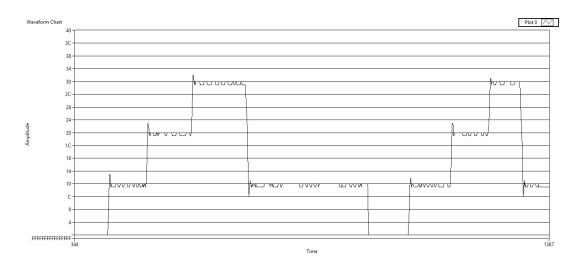

| Figura 57. Transmisión UART de todos los datos                        | 62 |

| Figura 58. Código de bloques de la recepción de datos en la interfaz  | 63 |

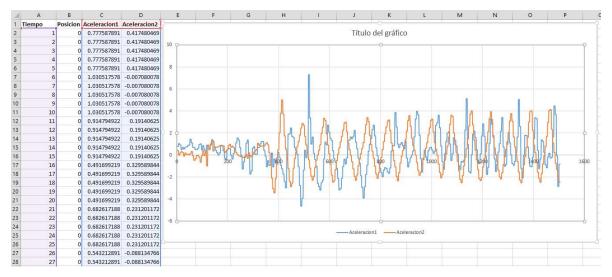

| Figura 59. Gráfica de comparación de aceleraciones                    | 64 |

| Figura 60. Gráfica a partir de los datos adquiridos                   | 64 |

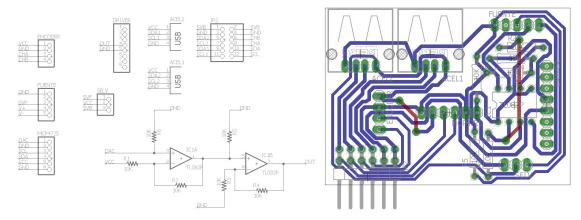

| Figura 61. Esquemático de la placa del SGV                            | 65 |

| Figura 62. Placa del SGV                                              | 65 |

| Figura 63. Conexión del controlador                                   | 65 |

| Figura 64. Controlador P con Kp=0.0625                                | 66 |

| Figura 65. Controlador P con Kp=0.25.                                 | 66 |

| Figura 66. Señal senoidal con controlador P                           | 67 |

| Figura 67. Señal senoidal con controlador PD                          | 67 |

## CAPÍTULO 1: INTRODUCCIÓN

El jueves 19 de septiembre de 1985, en la Cuidad de México, un terremoto con magnitud 8.1 en la escala de Richter azoto el centro del país a las 7:19am, con dos minutos de duración el sismo se convirtió en uno de los desastres naturales más difíciles en la historia este país. El número de estructuras que quedaron destruidas debido al suceso se estiman cerca de 2800, los edificios de entre 5 y 7 pisos resultaron los más afectados debido a que las vibraban naturalmente en el rango de frecuencias en los que vibraban los suelos rocosos de la ciudad. Entre las estructuras que se consideran casos excepcionales se encuentran La Torre Latinoamericana y la Torre Ejecutiva de Pemex (Centro de instrumentación y registro sísmico A. C., 2017).

La Torre Latinoamericana es un edificio de 181m de alto soportado por 361 pilotes de concreto, el edificio se diseñó para soportar un sismo de una magnitud 9 en la escala de Richter (Fomperosa, 2017). ¿Cómo es que saben que la estructura soportará?, los ingenieros civiles han trabajado en modelos matemáticos que predicen el comportamiento de las estructuras ante excitaciones externas; sin embargo, estos modelos no toman en cuenta muchas variables aleatorias que suceden durante un terremoto por lo que se han desarrollado máquinas con las que se pueden probar los modelos a escala de las estructuras, y así conocer un comportamiento más real de la estructura frente a un sismo (Carrillo et al., 2013).

A estas máquinas se les conocen como Mesas Vibratorias, la construcción de estos equipos ha permitido que los ingenieros civiles alrededor del mundo puedan desarrollar y mejorar técnicas de construcción con la finalidad de evitar catástrofes. Las mesas vibratorias actuales cuentan con sofisticados sistemas de control para reproducir de manera exacta una señal constante o un sismo anterior, con estos nuevos estudios resulta más apropiado validar que una estructura pueda soportar ciertas magnitudes de aceleración y determinar la frecuencia natural de los edificios, que es la frecuencia en la que la estructura presenta una mayor oscilación y dónde las posibilidades de colapso aumentan. Con bajas frecuencias las estructuras más altas oscilan con mayor facilidad mientras que en frecuencias más grandes las estructuras de menor altura son las que presentan las oscilaciones (Carrillo et al., 2013).

Estos dispositivos se pueden hallar en distintos tamaños, existen desde mesas para probar estructuras de unos cuantos kilogramos, o modelos sencillos, hasta mesas

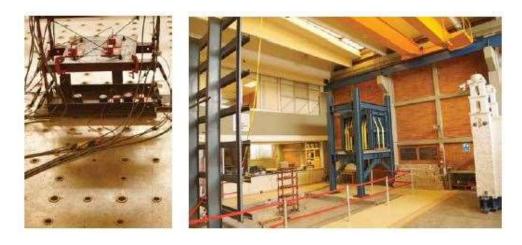

vibratorias dónde se construyen estructuras a escala real para revisar el movimiento exacto que tendrá la edificación. Existen mesas que se desplazan en los tres ejes, esto para asegurar que el movimiento telúrico se sienta en la estructura de una manera precisa. En la *Figura 1* se puede ver una mesa de gran tamaño para estructuras reales y en la *Figura 2* se aprecia una para modelos civiles a escala, como la que se pretende construir en este proyecto de tesis.

Figura 1. Mesa vibratoria a cargo de la Coordinación de Estructuras y Materiales de la UNAM.

Figura 2. Mesa vibratoria comercial Qanser, capacidad 7.5kg.

Un estudio de movimiento resulta incompleto si solo se observa dicho desplazamiento, las mesas vibratorias de mayor calidad incorporan a su sistema la adquisición de datos, que comúnmente refiere a la aceleración que se está aplicando a la estructura en distintos niveles. También en muchas ocasiones se mide el desplazamiento de la base de la estructura, esto para comparar dicho movimiento del suelo con la magnitud de la aceleración registrada. Para fines de evaluación de la estructura todas las variables medidas se comparan en gráficas dentro de una interfaz usuario-máquina, donde los expertos pueden determinar con base a su conocimiento si la estructura es apta o no para su construcción.

#### 1.1 Justificación

La necesidad de contar con una mesa vibratoria en la universidad reside en los beneficios que traerá para la docencia y el ámbito privado, pues estos dos tendrán la oportunidad de probar sus modelos y visualizar los efectos que sufren sus edificaciones en ensayos dinámicos, permitiendo a su vez el desarrollo e investigación de nuevas tecnologías útiles para evitar catástrofes.

El desarrollo de la mesa vibratoria dentro de la universidad asegura que la mesa cumplirá con los requisitos necesarios para llevar acabo las pruebas de laboratorio deseadas; contar con tecnología y desarrollo universitario nos permite disminuir sustancialmente los costos de fabricación.

Para lograr este cometido se diseñará un prototipo de una mesa vibradora controlada mediante un control en lazo cerrado de posición, esto nos asegurará un movimiento correcto en un eje para estresar los modelos que se deseen probar. Los ingenieros civiles podrán determinar, con una prueba de corta duración, la frecuencia natural de la estructura y su aceleración a dicha frecuencia en distintos niveles de ésta. Así los ellos determinarán si el modelo es apto para la construcción o requiere de un re-diseño que asegure que la estructura soportará en caso de un sismo.

## 1.2 Planteamiento del problema

El problema principal que busca solucionar el desarrollo de esta mesa vibratoria es la falta de este tipo de equipos en las universidades mexicanas. Sabemos que México es un

país altamente sísmico, los sismos son impredecibles por lo que se debe estar preparado ante un evento como estos. El desarrollo de estructuras sismo-resistentes es una solución a las catástrofes que trae consigo un fenómeno natural como este. Para que los ingenieros civiles puedan diseñar estructuras pensadas para esta clase de eventos se les debe proporcionar todas las herramientas posibles.

Los estudiantes de ingeniería civil de algunas universidades se ven en la necesidad de dedicar tiempo al desarrollo de mesas vibratorias manuales para validar algunos modelos estructurales que ellos realizan en la carrera, dichas mesas manuales no reproducen movimientos controlados, no reproducen patrones establecidos ni registran los datos de aceleración de los distintos niveles de la mesa vibratoria. Una mesa vibratoria que implementa un control de posición cubriría estos problemas pues los movimientos de la mesa se hacen controladamente y además ésta registra y despliega los datos en una interfaz para que el usuario pueda interpretarlos y así evaluar la estructura.

La falta de estos instrumentos de prueba en las universidades de debe al alto precio que estos equipos tienen en el mercado, pues es tecnología con gran tiempo de desarrollo y baja producción lo que los hace difíciles de conseguir. El desarrollo de un prototipo universitario permitirá, a los estudiantes de la UAQ, construir sus modelos y probarlos para comprender el comportamiento de las estructuras ante un sismo, además de probar distintos materiales y sus propiedades dinámicas ante los desplazamientos; en cuanto a los investigadores, les permitirá desarrollar nuevos métodos constructivos, y nuevas tecnologías sismo-resistentes.

El desarrollo de la mesa vibratoria en la Facultad de ingeniería posicionará a la Universidad Autónoma de Querétaro como una de las universidades líderes en el avance e investigación de estructuras sismo-resistentes en el país, pues pocas universidades mexicanas están de verdad preocupadas por el perfeccionamiento de nuevas tecnologías para evitar catástrofes urbanas.

## 1.3 Hipótesis y objetivos

## 1.3.1 Hipótesis general

Se puede diseñar y construir una mesa de vibraciones con un control de posición implementado en un motor BLDC para generar movimientos en una plataforma, esto nos permite realizar el estudio de aceleraciones presentadas en una estructura a partir del movimiento controlado de la base, para que los ingenieros civiles puedan evaluar daño

estructural en modelos a escala, identificar los problemas que la estructura puede presentar, probar nuevas tecnologías anti-sísmicas y validar diseños previos a su construcción.

## 1.3.2 Objetivo general

Desarrollar una mesa prototipo de vibraciones a través de un control de posición para motores de corriente directa sin escobillas (BLDC por sus siglas en inglés) y una interfaz de usuario que permite el control y el análisis de movimientos y aceleraciones en estructuras civiles.

## 1.3.3 Objetivos específicos

- Realizar en un FPGA un control de posición retroalimentado donde la señal real será adquirida mediante un encoder para asegurar que la plataforma se desplace la distancia requerida; el control permitirá trabajar empleando distintos modos de operación.

- Desarrollar un sistema de adquisición de datos y una interfaz usuario-máquina en el Software LabView para la visualización de los valores de aceleración que recopilen los sensores en distintas posiciones de la estructura civil; y desde donde se activarán los diferentes modos de operación del sistema y modificar sus características desde un formato amigable para el usuario.

- Diseñar y construir el prototipo de la mesa vibratoria empleando el software SolidWorks para tener documentado el diseño y establecer parámetros de la fabricación de la estructura de la mesa, permitiendo que esta sea replicable gracias a la documentación.

## CAPÍTULO 2: REVISIÓN DE LITERATURA

## 2.1 Antecedentes

A continuación se describen los trabajos realizados anteriormente en temas de control de posición en motores BLDC, implementación de controladores en FPGA e interfaces gráficas en LabView en la Universidad Autónoma de Querétaro. También se describe un poco del desarrollo de mesas de vibraciones a lo largo de la historia, se citan trabajos relacionados con el control de plataformas similares que sirvieron de apoyo en la realización del presente trabajo.

## 2.1.1 Antecedentes UAQ

En cuanto a los trabajos realizados por los estudiantes de la Facultad de ingeniería de la Universidad Autónoma de Querétaro se pueden resaltar algunas tesis sobre el control de motores con FPGA como es el caso del documento presentado por García-Cortés (2014) que desarrolla un controlador de movimiento para un robot PUMA en FPGA, es este documento el compañero realiza un controlador PD similar al presentado aquí con la diferencia de que su controlador es implementado en la computadora en lugar de en la tarjeta de desarrollo. Por otra parte los compañeros Arana y Mendoza (2011) desarrollaron un controlador de movimiento para una bancada de dos ejes, ellos realizaron una interfaz gráfica en el entorno LabView que tiene similitudes a la presentada en el presente documento. Otro documento importante es el que desarrolló Mendoza-Mondragón (2012) como tesis de maestría en el cual usa un FPGA para el control de movimiento de múltiples motores de DC, en ese documento rescatamos la implementación discretizada del controlador dentro del FPGA y el seguimiento de trayectorias que propone, en ese caso para generar perfiles de velocidad.

Existe bastante bibliografía en el repositorio universitario sobre trabajos con los temas de control de posición, implementación en FPGA y el uso de motores BLDC, los mencionados anteriormente son los más importantes en relación directa al presente trabajo y además presentan un reto directo al desarrollo del proyecto. No es ajeno en la

universidad el desarrollo tecnológico que las tarjetas de desarrollo FPGA representan hoy en día en la industria, y por ello muchos trabajos de gran importancia basan su desarrollo en esta tecnología.

## 2.1.2 Antecedentes generales

A lo largo de los años los sismos han golpeado territorio Mexicano en distintas ocasiones, algunas de ellas de tal magnitud que han dejado daños irreversibles en las edificaciones a lo largo del país. Tan solo en el 2017 se produjeron alrededor de 26,364 sismos, según el Servicio Sismológico Nacional, pero tan solo 4 de ellos fueron de magnitud entre 6 y 8.9 (Servicio Sismológico Nacional, 2016). Estos rompimientos repentinos de las rocas del interior de la tierra son imposibles de predecir, su efecto libera energía acumulada por la resistencia de la roca propagándose en forma de ondas en todas direcciones provocando el movimiento del terreno, afectando a las construcciones.

La mesa vibratoria es un dispositivo que reproduce movimientos sísmicos reales debidamente registrados para investigar el comportamiento dinámico y la respuesta sísmica de modelos estructurales de manera precisa (Unidad de Puentes, 2013). Carrillo, Bernal Ruíz, & Porras (2013) mencionan que las mesas vibratorias son aparatos que permiten simular, médiate una plataforma móvil, el movimiento que produce un sismo, los ensayos son dinámicos y de corta duración. Encima de la mesa se escala un modelo de una edificación y se prueba para conocer su comportamiento en distintas frecuencias, la mesa tiene el fin de ensayar nuevos sistemas constructivos, nuevos materiales, sistemas aisladores de base, disipadores de energía y para aprobar la construcción de las edificaciones. Además se colocan sobre el modelo una serie de instrumentos para monitorear su respuesta.

Las primeras mesas vibratorias comenzaron a desarrollarse en Tokio en el año 1893, se movían mediante una rueda mecánica con una manivela conectada a una plataforma sobre rieles. Unas décadas más tarde comenzaron a sustituirse los sistemas manuales por motores eléctricos, estas mesas fueron pieza clave para la realización de numerosos avances en la construcción de estructuras sismo-resistentes (Carrillo et al., 2013).

Las mesas vibratorias actuales comenzaron a partir de los avances logrados en la segunda guerra mundial. En estos días las mesas usan sistemas de control avanzados para simular sismos reales. Existen alrededor del mundo mesas vibratorias de gran tamaño con capacidad de movimiento en dos ejes que han sido fundamentales para el análisis, diseño y rehabilitación de edificios, puentes, entre otras estructuras de gran importancia.

Las mesas se clasifican en 3 principales grupos según Lehmann et al. (2012) en mesas de gran tamaño que permiten realizar ensayos sobre estructuras de tamaño y peso real; mesas de mediano tamaño las cuales son útiles para hacer pruebas dinámicas sobre modelos a escala y de un peso reducido; finalmente, las mesas pequeñas que son las que permiten realizar ensayos sobre modelos sencillos y pequeños.

Algunas universidades alrededor del mundo se han inclinado por el desarrollo propio de mesas vibratorias debido a los altos costos que manejas las empresas en este ramo y a la falta de variedad en ellas. La empresa líder en mesas vibratorias Quanser maneja la mesa de pruebas Shake Table II, siendo esta una de las más vendidas no tiene las características específicas para muchas aplicaciones (Peralta et al., 2013).

Muchos de los desarrollos tecnológicos en cuestión de mesas de vibraciones sísmicas presentan estructuras similares para el movimiento que consisten en la plataforma rígida que en algunos casos es sujetada por pistones hidráulicos como lo presenta Conte, et al. (2000) que son dispositivos para estructuras muy pesadas o reales debido al poder hidráulico. En una cuestión más didáctica podemos encontrar mesas de menor tamaño con un sistema de movimiento electromecánico que consta de motores y elementos mecánicos como los que se ven en Baran et al. (2010) ya que estos sistemas tienden a ser más exactos y a tener un mejor control lo cual beneficia a las pruebas a realizar.

México siendo uno de los países más activos sísmicamente solo cuenta con una mesa vibratoria considerada de gran tamaño en la Universidad Nacional Autónoma de México, a cargo de la Coordinación de Estructuras y Materiales. Ha estado activa desde 1997 y fue donada a ésta universidad por el Kajima Technical Institute después de ser elegida entre 8 universidades del mundo. Esta mesa está a disposición de los investigadores de la UNAM, instituciones de investigación y docencia, así como para el servicio a la industria (Ciencia UNAM, 2013).

La necesidad de continuar con el crecimiento de las ciudades y el temor de presenciar un sismo han orillado a los ingenieros civiles a diseñar y construir estructuras sismo-resistentes. Existen herramientas basadas en modelos matemáticos que los ingenieros usan para determinar el comportamiento de las estructuras en caso de un terremoto, pero dichos modelos no tienen en cuenta los efectos aleatorios que ocurren durante un sismo real, así que se ha optado por agregar al estudio de las estructuras sismo-resistentes distintas pruebas que complementen los modelos, como por ejemplo las mesas vibratorias, ensayos dinámicos y estáticos, con el fin de que los ingenieros puedan construir estructuras más confiables ante los desastres naturales (Lehmann et al., 2012).

## CAPÍTULO 3: METODOLOGÍA

### 3.1 Marco teórico

El control de motores es un campo ampliamente estudiado, en ellos se basa el movimiento de los sistemas robóticos de la actualidad, desarrollando sistemas integrados de funcionamiento general para aplicaciones en propósitos específicos, como el movimiento de un eje en un brazo robótico, la ubicación y movimiento de un cabezal en una impresora 3D o el posicionamiento de una bancada en una máquina de control numérico. Un sistema único de movimiento, como los anteriormente mencionados, se controlan de forma independiente, pero al ver trabajar distintos al mismo tiempo da la impresión de tener un movimiento en conjunto dentro de un dispositivo robótico.

Estas unidades independientes de movimiento se integran por ciertos componentes que convierten al conjunto en un llamado servosistema. Estos sistemas se componen de un servomotor, un dispositivo de detección de posición, un ensamble mecánico, un circuito amplificador y una unidad de control. El sistema generador de vibraciones funciona bajo el principio de un servosistema por el hecho de que estos dispositivos, que conjuntan lo electrónico y lo mecánico, trabajan con gran eficiencia y precisión.

#### 3.1.1 El motor BLDC

Uno de los componentes anteriormente mencionados que componen al servosistema es el motor en sí. Existen diferentes tipos de motores con los que trabajan los servosistemas, éstos se pueden dividir en dos grandes grupos. Los motores de Corriente Alterna (CA) que son en los cuales la velocidad del motor es determinada por la frecuencia del voltaje aplicado y el número de polos magnéticos, éstos tienen una ramificación hacia la forma en la que operan, éstos puede ser síncronos o asíncronos.

Por otro lado se encuentran los motores de Corriente Directa (CD) en los cuales la velocidad es proporcional al voltaje suministrado a una carga constante, éstos se pueden

dividir en dos diferentes grupos los que trabajan con escobillas y los motores sin escobillas llamados motores BLDC (Brushless Direct Current).

Los motores con escobillas funcionan mediante el uso de un conmutador, que es un switch electrónico que periódicamente invierte la dirección de la corriente en el rotor. Éste es un cilindro con segmentos metálicos que tienen contacto con las escobillas que permiten la polarización del circuito en el rotor generando un campo magnético cambiante en éste. El motor con escobillas más usado es el de imanes permanentes que actúan con el campo magnético del rotor haciendo girar la flecha.

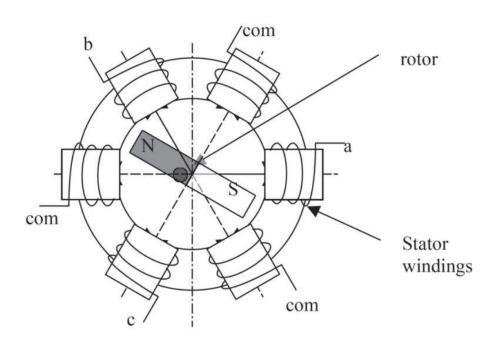

Por otra parte se encuentran los motores BLDC tienen imanes permanentes de distintos materiales en el rotor y podemos encontrar desde dos hasta ocho pares de polos alternados entre Norte (N) y Sur (S); mientras que en el estator tienen embobinados que son conmutados de acuerdo a la posición del rotor con respecto al estator (*Figura 3*). En este tipo de motores se pueden encontrar configuraciones para su funcionamiento con una, dos y tres fases, de acuerdo a esta configuración el estator presenta cierto número de embobinados, siendo los de tres fases los más populares y los más comúnmente usados.

Figura 3. Diagrama interno de un motor BLDC.

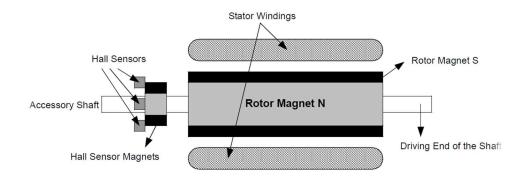

Los BLDC son motores síncronos, esto significa que el campo magnético del estator y el campo magnético que genera el rotor giran a la misma frecuencia. A diferencia de los motores con escobillas, la conmutación de un motor BLDC se hace electrónicamente. Para hacer girar el rotor las bobinas del estator se deben de energizar con cierta secuencia. Los motores BLDC con frecuencia cuentan con sensores de efecto Hall unidos a la flecha del rotor (*Figura 4*). Cada vez que los polos magnéticos de rotor pasan a través del sensor Hall

entregan una señal en alto o en bajo indicando que el Norte o el Sur del polo está pasando a un costado del sensor. Usando la combinación de tres sensores de efecto Hall se determina con exactitud la secuencia de conmutación.

Figura 4. Partes del motor BLDC.

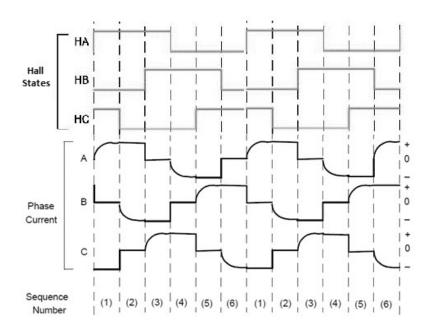

Cada secuencia de conmutación en el motor BLDC mantiene una bobina energizada positivamente (La corriente entra a la bobina), la segunda se polariza negativamente (La corriente sale de la bobina) y la tercera no está energizada, así el torque es generado de acuerdo a la interacción de los campos magnéticos formados en el estator junto a los imanes permanentes en el rotor. Para hacer que el rotor continúe moviéndose las bobinas deben conmutar en una secuencia de 6 pasos (*Figura 5*).

Figura 5. Comportamiento de las fases de un motor BLDC.

Este tipo de motores se usan principalmente en aplicaciones con constantes arranques y frenados, así como constantes cambios del sentido de giro, demandando mucho torque especialmente en los arranques debido a la inercia que la carga le genera al rotor. Las ventajas de este motor recaen en el bajo mantenimiento que requieren así como en su larga vida útil; los rangos de velocidad que manejan son muy amplios generando poco ruido con gran eficiencia.

## 3.1.2 El amplificador

Para conmutar de manera rápida y precisa se requiere de un dispositivo electrónico que energice las bobinas del rotor a medida que toma la lectura de la posición del rotor dada por los sensores de efecto Hall. Para eso se requiere de un amplificador, este dispositivo se encarga de activar las bobinas en la secuencia correcta, dada por los 6 pasos mostrados en la *Figura 5*. Esta energización requerida de las bobinas debe de crearse a través de un voltaje alto por lo que el amplificador debe de trabar con una tensión diferente a la usada por lógica que controla la activación y la lectura del estado que entregan los sensores Hall.

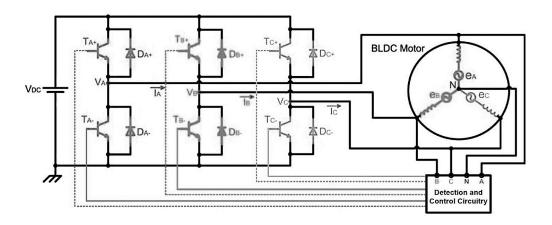

Los amplificadores internamente cuentan con un arreglo de transistores (Figura 6) que conmutan, con señales digitales, la activación de grandes voltajes de corriente directa. Es un punto a contrastar que un motor BLDC se tiene que energizar con una fuente de alimentación de frecuencia variable y tres fases de corriente alterna para su funcionamiento. El amplificador activa las líneas de suministro de la corriente directa con la secuencia y en la dirección que muestra la *Figura 5*, creando la señal de corriente alterna necesaria para el funcionamiento del motor; La frecuencia de esta señal dependerá de la velocidad a la que el sistema digital conmute sus salidas.

Figura 6. Arreglo interno para la conmutación de las fases.

Típicamente los amplificadores son suministrados con voltaje de CD y una señal de voltaje variable entre -10v y 10v, este voltaje funciona como referencia para la velocidad de salida del motor, el voltaje negativo significa un cambio de giro, mientras que el voltaje en cero equivale a que el motor se mantenga estático.

## 3.1.2.1 Acoplamiento de señales

Como se comentó, el sistema de amplificación típico recibe señales analógicas que van de los 10v hasta los -10v, mientras que los sistemas electrónicos, que típicamente hacen el procesamiento de datos y control, trabajan con señales lógicas de 5v por lo que en medio de ambos sistemas debe de haber un circuito que transforme la señal lógica en una análoga.

El primer requerimiento para acoplar las señales es lograr que es sistema de control envíe su señal de corrección (*Capítulo III.2.5 Unidad de control*) de manera analógica, esto el sistema de control no lo puede realizar debido a que sus señales son digitales, así que es necesario emplear un *Convertidor Digital-Analógico* (DAC, por sus siglas en inglés). El DAC es un dispositivo electrónico que típicamente trabaja con el mismo voltaje que el sistema electrónico, de 0 a 5v de DC, así que sus valores analógicos tendrán estos límites de voltaje; otro dato importante a conocer sobre los DAC es la resolución, y ésta está dada por la cantidad de bits que entran al dispositivo para controlar la salida.

Figura 7. Diagrama interno del DAC0800.

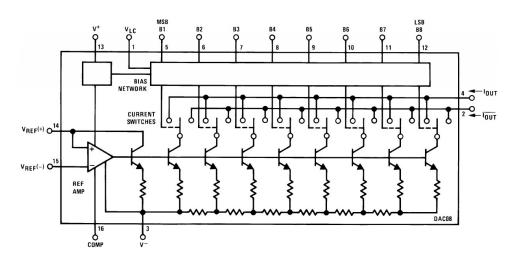

La resolución de un DAC es simplemente la máxima diferencia de potencial que alcanza a la salida, dividido entre el número *decimal* máximo de entrada (*Ecuación 1*), donde podremos ver el voltaje por unidad, así calcularemos el número *binario* necesario para cierta cantidad de voltaje. Los convertidores reciben una señal de una longitud definida de

forma digital, por lo tanto, existen dos tipos de Convertidores Digital-Analógico, los que trabajan con un bus de datos en paralelo, lo cual significa que tiene tantas entradas como bits de resolución, en la *Figura 7* podemos observar el DACO800 de 8 bits de resolución, como se puede observar tiene una gran cantidad de entradas lo que podemos traducir en la misma cantidad de salidas del sistema electrónico que lo controla; Por otra parte también podemos encontrar comercialmente los DAC que trabajan mediante algún protocolo de comunicación, éstos requieren de una programación más extensa pero ahorran puertos de entradas y salidas digitales al sistema electrónico de control.

$$Resolución = \frac{Diferencia\ Máxima\ de\ potencial}{2^{n\'umero\ de\ bits}} \tag{1}$$

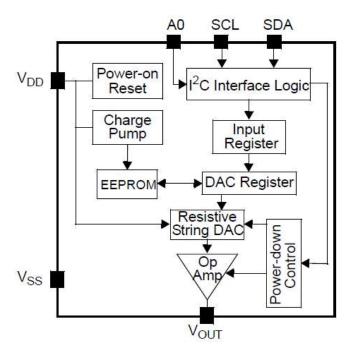

Se pueden encontrar distintos tipos de protocolos de comunicación para estos dispositivos, pero uno de los más comunes es sin duda el protocolo I<sup>2</sup>C (Se ve más a fondo en el *Capítulo III.2.6.1*), mediante este protocolo podemos controlar un DAC con tan solo dos cables de comunicación digital, los llamados SCL y SDA (Serial Clock y Serial Data). En la *Figura 8* se puede observar un diagrama de bloque que explica los componentes internos de un DAC I<sup>2</sup>C.

Figura 8. Diagrama de bloques de un DAC I<sup>2</sup>C.

Una vez que el voltaje es controlado analógicamente se requiere que este trabaje tanto en valores de voltaje negativos como positivos, algo que un DAC como el anterior no puede realizar. Una de las opciones más comunes es usar otro Convertidor Analógico-Digital con su salida de voltaje invertida, y así controlar tanto los voltajes positivos como los negativos.

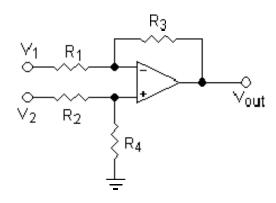

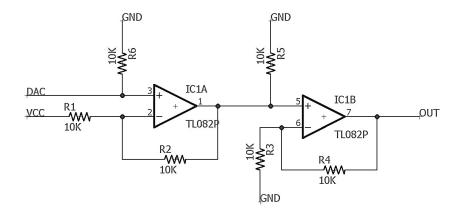

Existe otra solución a este problema y es el uso de *Amplificadores Operacionales* (OpAmp, por su acrónimo en inglés). Una configuración para OpAmp que nos serán muy útil para esta aplicación es usarlo como restador (*Figura 9*) nos permite hacer la diferencia entre dos tensiones en sus entradas, además de que si usamos ciertas resistencias podemos amplificar la señal a la salida. Para conseguir que el voltaje analógico de 0 a 5v se transforme en una señal de -10v a 10v seccionaremos en dos partes el proceso pues la configuración no nos permite lograrlo con un solo arreglo, por lo que se requiere de un arreglo en cascada de dos Amplificadores Operacionales.

Figura 9. Circuito OpAmp restador.

Primero necesitamos conocer las ecuaciones que gobiernan el comportamiento de ésta configuración para así verificar que el proceso funciona. La *Ecuación 2* indica cómo es el voltaje a la salida del OpAmp. La configuración inicial tienen que lograr que la señal de voltaje trabaje desde valores negativos hasta valores positivos, para esto le restaremos un voltaje a la señal que sale del DAC, así obtendremos una señal de -5v a 5v; La segunda parte no restará nada a la señal, pero la amplificará dos veces para obtener a la salida la señal que necesitamos.

$$V_{out} = V_2 * \left(\frac{R_4}{R_2 + R_4}\right) * \left(1 + \frac{R_3}{R_1}\right) - \left(V_1 \frac{R_3}{R_1}\right)$$

(2)

Consideremos para ambas configuraciones los siguientes valores en las resistencias:

$$R_1, R_3, R_4 = 10K\Omega$$

,  $R_2 = 0\Omega$

Con estos valores propuestos podemos armar el circuito de la *Figura 10*, analizándolo y aplicando la *Ecuación 2* podemos observar cómo se comporta el circuito, bajo una ecuación final. El Integrado propuesto para esta aplicación es el TL082, pues internamente tiene dos Amplificadores Operacionales.

Figura 10. Circuito de acoplamiento DAC-Amplificador.

Aplicando los valores de las resistencias a la *Ecuación 2*, obtenemos:

$$V_{out} = V_2 * \left(\frac{10K\Omega}{0 + 10K\Omega}\right) * \left(1 + \frac{10K\Omega}{10K\Omega}\right) - \left(V_1 \frac{10K\Omega}{10K\Omega}\right)$$

$$V_{out} = V_2 * 2 - V_1 \tag{3}$$

La *Ecuación 3* es la ecuación para cada uno de los Amplificadores, a continuación sustituiremos el  $V_2$  en una ecuación con el  $V_{out}$  de otra, justo como se observa el circuito de la *Figura 10*, también usaremos los valores de ambos  $V_1$  que en la primera ecuación vale 5v y en la segunda ecuación vale 0v pues está conectada a GND. El primer circuito se denota con el sufijo "a" y el segundo circuito con el sufijo "b".

$$V_{out b} = (V_{2a} * 2 - V_{1a}) * 2 - V_{1b}$$

$$V_{out} = (((V_{DAC} * 2) - 5v) * 2) - 0v$$

(4)

| Voltaje proveniente del DAC | Voltaje de salida al Amplificador |

|-----------------------------|-----------------------------------|

| 5v                          | 10v                               |

| 4v                          | 6v                                |

| 3v                          | 2v                                |

| 2.5v                        | 0v                                |

| 2v                          | -2v                               |

| 1v                          | -6v                               |

| 0v                          | -10v                              |

Tabla 1. Comportamiento de los voltajes a la salida del circuito.

La *Ecuación 4* gobierna el comportamiento del circuito después del DAC y antes del amplificador, con ésta ecuación podemos obtener la *Tabla 1* que nos muestra el comportamiento de salida con diferentes entradas. Notemos que el valor de salida de 0v se encuentra con el valor de 2.5v proveniente del DAC, por lo que podemos concluir que idealmente el estado dónde el motor está estático, porque no recibe voltaje, es el valor medio de la resolución de nuestro DAC.

## 3.1.3 Encoder

Es necesario para controlar la posición de un motor tener un valor equivalente al ángulo al que se encuentra el rotor de nuestro motor, una forma típica y sencilla de conocer este parámetro es bajo el uso de un sensor de posicionamiento óptico conocido como encoder rotativo. Es posible también conocer la posición del rotor con el uso del sensor de efecto Hall integrado en un motor sin escobillas, pero para esto se requiere de un análisis extra de los datos entregados por el sensor por lo que un encoder es lo más útil y eficiente.

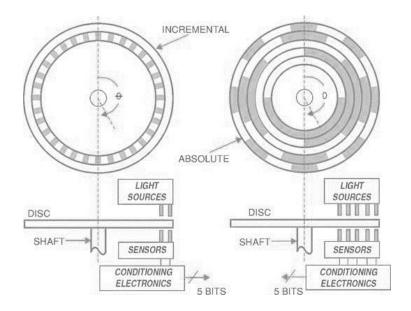

Se pueden encontrar encoder ópticos tanto Absolutos como incrementales (*Figura 11*). Los encoder ópticos operan con el uso de un disco con ranuras y elementos de reflexión, que dependen de un emisor y un receptor; El emisor pasan su haz de luz a través del disco, si el receptor detecta el haz significa un estado lógico, el caso contrario representará el estado lógico complementario.

Figura 11. Comparación de encoder incremental y absoluto.

Los encoder Absolutos tienen un disco donde la combinación de sus muescas en una posición específica representa un ángulo único o una porción de circunferencia, así que un arreglo lógico es la salida que se obtiene de éste tipo de encoder. Los encoder Absolutos tienen la ventaja de conocer la posición en la que se encuentran incluso después de haber sido des-energizados pues la combinación de sus salidas les permiten reconocer ese dato al energizarse.

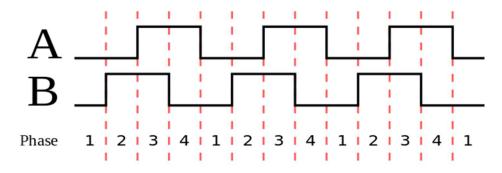

Por otra parte los encoder Incrementales tienen un disco con múltiples ranuras sobre una altura específica del disco y equidistantes entre ellas (un patrón periódico), a través del disco pasan únicamente dos haces de luz que están desfasados entre ellos, obteniendo a la salida dos señales cuadradas desfasadas en el tiempo (*Figura 12*). La secuencia en que un dispositivo lee esta señal determina la dirección que el disco tiene y por consecuencia lo que esté acoplado a él.

Figura 12. Secuencia del encoder.

Una ventaja de los encoder Incrementales es que pueden contar las vueltas completas que el rotor ha dado, las señales A y B anteriormente mostradas (*Figura 12*) son las salidas principales de nuestro encoder, muchos encoder presentan una tercera salida (Señal C) que indica con un pulso en alto cada que el encoder ha pasado por un punto en específico, o en otras palabras, cada que el rotor ha dado una vuelta completa.

Algunos parámetros importantes para trabajar con este tipo de encoder es la cantidad de ranuras que presenta el disco, pues esta será exactitud con la que podremos posicionar el disco, o sea, el ángulo al que se encuentra el rotor. Al conocer esta cantidad de ranuras podemos calcular cuánto es el ángulo mínimo de movimiento que nos permite el encoder, pues una precisión más grande será prácticamente imposible, el dato se conocerá dividiendo los 360° presentes en una circunferencia entre la cantidad de ranuras. Al conocer la cantidad de ranuras también podemos conocer cuando el encoder haya pasado en un punto específico, sin la necesidad de contar con la *Salida C*, solo hace falta que el dispositivo que recibe la señal del encoder cuente hasta el número de ranuras para saber que se dio una vuelta completa.

El conteo no es tan sencillo como parece pues no se trata solo de contar cuando la señal del encoder tiene un cambio en su estado, pues se trata de conocer en que paso está de la señal recibida en las terminales A y B conociendo cual fue el estado anterior para compararlos y conocer la dirección. Esto ocasiona que cada ranura del encoder tenga cuatro estados, y por ende el conteo de las señales se multiplique por cuatro. Con esto podemos obtener las siguientes formulas.

$$Presición (°) = \frac{360°}{Número de \ ranuras * 4}$$

(5)

Cuentas por vuelta =

$$N$$

úmero de ranuras \* 4 (6)

## 3.1.4 Dispositivo mecánico

Cuando se controla la posición a la que gira el rotor del motor es útil conocer la aplicación del servomotor, pues ésta determinará una serie de elementos mecánicos que usarán el movimiento rotatorio del eje y lo transformarán para el movimiento de una estructura mecánica. Para poder generar una oscilación en cualquier cuerpo tal como lo hace un sismo se requiere que la estructura base del cuerpo tenga movimiento. El sistema requerido para una aplicación dónde la base mueve objetos sujetados a él, se asimila a una aplicación muy conocida cómo lo son las máquinas de control numérico.

El sistema base de movimiento de máquinas como esta es tan común que tiene una extensa aplicación en la industria, y en otras aplicaciones, las encontramos en maquinas CNC, impresoras 3D, cortadoras laser, entre otras. El movimiento de una plataforma metálica se tiene que hacer transformando el movimiento rotacional en un movimiento lineal, el elemento más comúnmente usado es el tornillo de bolas.

El tornillo de bola consiste en una barra metálica con un corte en espiral que funciona como guía para un bloque que se desliza linealmente a lo largo de la barra, el bloque logra avanzar debido a un arreglo de balines internos que giran dentro de los canales del tornillo empujando el bloque que tiene dentro un corte complementario similar al de la barra (*Figura 13*).

Figura 13. Interior del bloque de deslizamiento.

La cantidad de avance que el bloque tendrá siempre depende de la cantidad de espiras que contenga el total del largo del tornillo. Esto logra, según la aplicación, que podamos definir la cantidad de avance que se requiere linealmente por cada vuelta, con este dato inicial se puede inferir la cantidad de vueltas necesarias para completar una unidad de movimiento.

En el caso particular de la aplicación aquí desarrollada se requiere cierta cantidad de información mecánica para controlar la posición de la plataforma. Anteriormente se planteó la *Formula 6* con la que podemos obtener la cantidad de pulsos que recibiremos del encoder por cada vuelta del rotor, ahora es necesario calcular la cantidad de pulsos que obtendremos para mover la plataforma una unidad de longitud. A partir de ello y con la ayuda de un dato de diseño que es la cantidad total de movimiento requerida por la aplicación podemos inferir la cantidad de pulsos que obtendremos, como entrada en el sistema de control, por el desplazamiento entre los límites máximos de la plataforma.

Cuentas por unidad

= Cuentas por vuelta \* Vueltas por unidad de desplazamiento (7)

Valor máximo

= Cuentas por unidad \* unidades de desplazamiento requeridas (8)

#### 3.1.5 Unidad de control

En general el control trata de lograr que un sistema reaccione y cumpla con los parámetros que el usuario requiere para la aplicación en la que se encuentra mediante

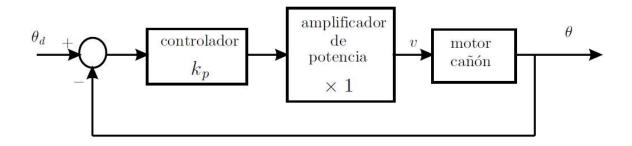

métodos matemáticos. En la aplicación que estamos desarrollando es necesario hacer un control de posición en el motor para obtener desplazamientos controlados de la plataforma. En general el control se basa en la diferencia que hay entre la variable medida y la variable deseada, por ejemplo, para la posición de un motor se obtiene el dato del encoder que equivale a la posición actual y se obtiene un dato suministrado por el usuario que equivale a la posición deseada; La diferencia de estas dos variables es el *Error*, dato principal de la unidad de control. El error es manipulado internamente para que a la salida de la unidad de control haya una señal de corrección que haga que el motor llegue a la posición deseada.

Como se explicó anteriormente, la plataforma obtiene su desplazamiento de la transformación de movimiento rotacional de un motor, manteniendo la premisa de que si el motor gira en sentido horario la placa se moverá a la derecha, caso contrario, si el motor gira en sentido anti horario la plataforma se moverá a la izquierda. El sentido de giro del motor está controlado por el amplificador que recibe un señal donde el voltaje positivo (hasta 10V) hace girar el motor en sentido horario, el voltaje negativo (hasta -10V) lo hace girar en sentido anti horario, por último, suministrarle una diferencia de tensión de 0V hace que el motor no se mueva.

La unidad de control también tiene la función de interpretar los datos que recibe de las salidas A y B del encoder, estas señales las transforma en un número entero para su fácil comprensión, donde el valor máximo de éste número es el calculado en la *Ecuación 8*, así la unidad sabe en todo instante la *posición real del motor* ( $\theta$ ) y recibe mediante algún método un valor asignado por el usuario que se denomina *posición deseada* ( $\theta d$ ). El control busca que  $\theta = \theta d$  en todo momento. Con esto podemos determinar que el error se calculará de la siguiente manera:

$$e = kp \left(\theta d - \theta\right) \tag{9}$$

Donde *Kp* es una constante positiva. Podemos observar que para la aplicación, tal como se describió anteriormente, el *error* es directamente proporcional al voltaje de salida, pues cumple con los requerimientos, el voltaje como el error pueden ser positivos o negativos, además de ser cero cuando la *posición real* alcanzó la *posición deseada*.

Figura 14. Diagrama a bloques del sistema de control de un cañón antiaéreo.

El diagrama a bloques de la *Figura 14* representa gráficamente el funcionamiento general del control de posición y sus partes a desarrollar, se observa una constante Kp que se define como la ganancia proporcional está multiplicando al valor de voltaje con el que se alimenta al motor, por lo tanto el motor girará más rápido o más lento dependiendo del valor de la constante. El tipo de respuesta de la posición con respecto del tiempo varía según sea el valor de Kp. Con un valor mayor la posición llegará más rápido al valor deseado pero el sobrepaso de la señal va a ser también grande pues la velocidad con la que el motor se acerca a  $\theta d$  es grande y al sistema le cuesta frenar a tiempo para cambiar de sentido y estabilizarse; con una Kp baja, el sistema tiende a ser más lento, pero con un sobrepaso menor o incluso nulo.

Un punto importante del diseño de un sistema de control es la estabilidad, para afectar a un sistema de control se consideran perturbaciones externas a cualquier movimiento que altere la estabilidad del estado estacionario, en otras palabras, se requiere que la posición del eje se mantenga en la *posición deseada* aunque externamente algo esté alterando al sistema. Muchos sistemas mecánicos están pensados para trabajar en distintos ejes pero en algunos ejes existen fuerzas constantes que actúan sobre el sistema, la gravedad actúa sobre un eje que es perpendicular al eje de trabajo de la plataforma, por lo que en análisis estático no actúa sobre el movimiento de la placa de nuestro sistema alterándolo en el estado estacionario, se dice que el error en estado estacionario es cero para un sistema como este que trabaja sobre el eje horizontal.

Las señales de movimiento que se quieren estudiar son variantes con el tiempo, es posible que el controlador sea capaz que realizar cambios en su posición deseada para adaptarse a trayectorias de posición, una forma de ver cualquier señal en el tiempo es con muestras cada tiempo constante. La señal de las muestras tendrá una apariencia escalonada si el tiempo entre muestras es muy largo. Podemos de forma sencilla definir cuantas muestras nos son suficientes para conseguir los resultamos que deseamos.

La señal que se plantea, que cuenta con algunas características en común con los sismos, es la senoidal, pues nos ofrece dos rasgos importantes, la *frecuencia* y la *amplitud*. Para enviar la magnitud al sistema de control se requiere que la señal senoidal sea seccionada para que asemeje una entrada de una forma escalonada. El sistema de control tiene que ser lo suficientemente rápido, como mínimo, para que el tiempo de subida de la señal alcance la posición del escalón siguiente para poder realizar la trayectoria senoidal correctamente, manteniendo los valores de *frecuencia* y *amplitud* que se desean. Bajo este principio de movimiento es posible replicar casi cualquier señal variante en el tiempo, la limitante que tiene es la velocidad del motor. Una diferencia en la posición tan grande, que la velocidad máxima del motor no pueda alcanzar en el tiempo antes de que otro valor de posición sea establecido, será el caso en el que no se pueda seguir con exactitud la trayectoria deseada.

## 3.2 Descripción de hardware FPGA

El sistema que realiza el control, el monitoreo las señales, el envío de datos para graficar, el control del voltaje de salida, y los distintos protocolos de lectura de datos son actividades que se deben ejecutar al mismo tiempo para no perder un solo dato. Los microcontroladores dependen de la velocidad de un cristal para ejecutar cada instrucción de lo programado, como es de forma secuencial la ejecución de las instrucciones en el sistema puede ser más lenta. Un Field Programmable Gate Array o FPGA es un dispositivo capaz de modificar la configuración interna de su sistema para obtener, en un tic de reloj, múltiples tareas sencillas, así que la cantidad de estas compuertas determina la cantidad de procesos en paralelo que puedas tener. Esta característica permite que en un solo sistema de control pueda hacer el cálculo del error en cada instante ejecutando una acción correctiva, al mismo tiempo que realiza otras tareas como el envío de datos de posición y aceleración a la computadora para que se grafiquen; otra tarea que el sistema principal debe realizar es la lectura de la aceleración, que es un dato importante que puede ayudar a los ingenieros civiles a entender que sucede en la estructura al momento de un sismo.

## 3.2.1 Protocolo I<sup>2</sup>C

Se necesitan programar algunos protocolos en la tarjeta FPGA para comunicarse con los dispositivos electrónicos que controlan la parte mecánica, como se comentó anteriormente (Capitulo III.1.2.1 Acoplamiento de señales) el amplificador necesita de una señal transmitida en el protocolo I<sup>2</sup>C para poder ejecutar las tareas de conversión de datos digitales a una señal analógica.

Figura 15. Trama básica del protocolo I<sup>2</sup>C.

Este protocolo de transmisión de datos es síncrono por lo que se requiere de una señal de reloj constante entre el elemento maestro y el elemento esclavo. El dato que se quiere enviar se transmite mediante una sola línea de datos a la frecuencia que marca la señal de reloj para que el elemento que recibe la señal pueda interpretar la trama de datos enviada, este dato se requiere que se envíe con una trama específica. Cuando se definen los componentes que se utilizarán se puede consultar si existen tramas específicas para que la comunicación entre el dispositivo del fabricante y el FPGA sea la adecuada. El envío de datos se debe realizas con algunas reglas específicas del protocolo, como: las condiciones de START y STOP, el estado de ACK para la confirmación de lectura y estado lógico para lectura y escritura. Se puede observar una representación gráfica de cómo es el protocolo en la *Figura 15*.

Figura 16. Bloque del protocolo I<sup>2</sup>C.

El bloque que se desarrolló para la comunicación I<sup>2</sup>C genérica en el FPGA es el mostrado en la *Figura 16*, dónde podemos observar un bit RST, equivalente a la señal que reinicia el bloque, es una señal que cuando detecta un cero realiza su función de reinicio, el bit CLK es la señal que se obtiene del cristal del FPGA, este bit gobernará la velocidad con la que se ejecuta cada instrucción, el bit STT es la señal que cuando se detecta en alto inicia el proceso de transmisión, aquí se usa un Timer para enviar pulsos a una frecuencia determinada para escribir los datos, y la señal DTO que son 12 bits en paralelo que representa el valor que se quiere enviar. Como salidas se tiene el SCL o Serial Clock, que envía una señal cuya función es sincronizar el proceso, y como caso especial tenemos la señal SDA o Serial Data que es una señal de entrada/salida, el dato se enviará y mediante esta vía también recibirá una respuesta del esclavo. El sistema principal pone la salida en alta impedancia, que es un estado donde el circuito maestro permite que otro sistema (El esclavo) utilice el canal para enviar su respuesta.

Figura 17. Trama del protocolo para el circuito MCP4725.

La Figura 17 es la trama de datos que requiere en específico el circuito MCP4725 que es un DAC de 12 bits de resolución que entrega a la salida un valor máximo de 5v, pues este es el voltaje con el que se alimenta el circuito. La trama requiere de una dirección de esclavo la cual se puede conseguir en la hoja de datos del fabricante, remontándonos al Datasheet del MCP4725 obtenemos que A2 y A1 deben de estar en un estado lógico bajo ('0'), y A0 dependerá del estado lógico que nosotros deseemos, esto se hace con la finalidad de que si el usuario desea usar un segundo DAC de este tipo pueda controlar la salida de cada uno independiente del otro. Para este caso se ha decidido poner el bit A0 a un estado lógico bajo pues así lo entrega el fabricante, el último bit es el estado de lectura/escritura, como deseamos enviarle un dato para convertirlo en una salida analógica debemos escribir en el DAC, según la misma figura (Figura 17) el estado lógico para escribir es bajo, por lo tanto, el primer byte para enviar sería "11000000", seguido de una alta impedancia para que durante ese tiempo podamos recibir la respuesta del esclavo.

El segundo byte en la trama es de configuración para el DAC, la trama que a usar es "01000000", los primero 3 bits son el comando de escritura, como solo queremos escribir en el DAC un valor para que se refleje a la salida no hace falta guardarlo en la EEPROM, que es la memoria interna del DAC, por lo que únicamente se envía un "010". Los dos bits siguientes no importan en la trama por lo que se puede enviar cualquier valor, igual que el último bit; Los bits 2 y 3, de derecha a izquierda, son para activar el Power-Down mode, lo cual no necesitamos y por lo tanto van en cero. Después de enviar este byte se requiere que el canal SDA tenga un estado lógico de alta impedancia una vez más para recibir la respuesta del esclavo.

Los siguientes 12 bits equivalen al dato que queremos enviar como señal de control, estos se dividen en 2 partes, pos primeros 8 bits, los más significativos formarán un byte seguido de un lapso de alta impedancia, le continuarán los siguientes 4 bits menos significativos acompañados de 4 bits más, los cuales su valor no importa por lo que podemos enviar ceros. Para finalizar la transmisión se deja el canal en alta impedancia otra vez para recibir la respuesta del esclavo.

El esclavo responderá a cada bit con una señal en bajo si ha recibido correctamente la trama. Seguido de eso se enviará el estado de STOP que es una combinación del canal SCK y SDA.

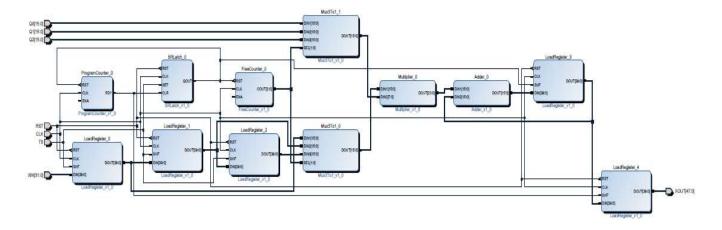

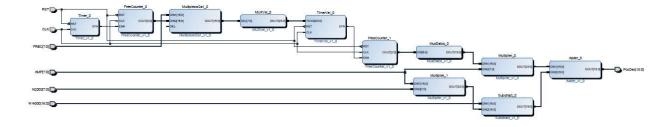

Figura 18. Diagrama a bloques del protocolo I<sup>2</sup>C.

La máquina de estados (FSM\_0) de la *Figura 18* es la que controla cómo funcionará el protocolo I²C, ésta ejecuta una acción cada que recibe un pulso del Timer\_0, envía un dato almacenado en el MUX\_0 cada que se requiere para completar la trama antes mencionada. Hasta ahora el protocolo I²C desarrollado solo escribe datos en el esclavo pero no puede leer datos, requerimos también que haga esta acción pues es necesario adquirir el valor de la aceleración que nos proporcionan los acelerómetros que instrumentan la edificación y con la cual los ingenieros civiles pueden realizar su estudio de manera adecuada.

Los acelerómetros elegidos para esta aplicación son los MPU-6050, los cuales pueden registrar la aceleración en los tres ejes con una resolución de 16bits por eje, con rangos de trabajo ajustables de ±2, 4, 6, 8 y 16g. La trama a enviar es la mostrada en la *Figura 19* según el Datasheet del instrumento.

| Master | S   | AD+W |     | RA  |     | S   | AD+R |     |      | ACK |      | NACK | Р   |

|--------|-----|------|-----|-----|-----|-----|------|-----|------|-----|------|------|-----|

| Slave  | 9 9 | - 3  | ACK | 8 8 | ACK | 9 9 |      | ACK | DATA | 8 9 | DATA |      | 8 8 |

Figura 19. Trama del MPU-6050.

Como se puede notar, la trama tiene diferencias significativas incluso es más larga, pero trabaja con la misma base que tiene el MCP4725, por lo que se requiere de pequeñas modificaciones al diagrama a bloques de la *Figura 18* para poder funcionar en este otro dispositivo. La nueva trama comienza con la condición de START de la misma manera que en caso anterior, después, el primer byte será la dirección del esclavo seguida del bit de escritura, la dirección del acelerómetro es "110100X" siendo la X el estado al que se pone el pin A0 del circuito. Como en el caso anterior el último bit se pone en un estado lógico bajo que equivale a escritura, después el sistema debe poner el canal SDA en alta impedancia para permitirle al esclavo responder con un estado lógico en bajo (ACK). La trama continúa con un byte con la dirección del registro que se desea leer, para esto se requiere consultar los registros del acelerómetro para saber qué datos se desean obtener, en el caso particular de nuestra aplicación debemos leer la aceleración en un solo eje.

Recordemos que el acelerómetro que estamos usando nos entrega un valor de 16 bits, por lo que la lectura debe hacerse de dos registros, es complicado e innecesario realizar dos lecturas, una para cada registro, por lo que la configuración de la trama nos permite leer múltiples registros consecutivos. Por ejemplo, los registros de la aceleración en el eje Y son 0x3D para la parte alta y 0x3E para la parte baja. El byte del registro que usaremos es "00111101" que refiere a la parte alta del dato, una vez enviado el sistema debe esperar la respuesta del esclavo.

La trama de la *Figura 19* indica que se debe presentar, una vez más, la condición START, seguida de la dirección del esclavo pero acompañada del último bit en alto refiriendo a la lectura ("110100X1"), seguido de esto el sistema espera una respuesta del esclavo en bajo y comienza la lectura de los primeros 8 bits del dato, durante la lectura el canal SDA debe permanecer en alta impedancia para permitirle al esclavo usarlo para enviar los datos. Como ahora es el esclavo el que envía la información el sistema debe contestar al final de cada lectura con un estado en bajo, el esclavo continuará enviando los valores de los siguientes registros hasta que el sistema maestro responda con un valor en alto, o como la *Figura 19* lo llama, un ACK negado (NACK). Finalmente la trama termina con la condición STOP.

Toda esta nueva trama se debe configurar con la secuencia y valores anteriormente explicados en el bloque MUX\_0 de la *Figura 18* así el sistema los enviará en el orden correcto. Una adición que se le hace al diagrama es un bloque llamado "*Registro Serial Paralelo*" que tiene la función de almacenar los datos que está leyendo el protocolo I<sup>2</sup>C, los lee de forma serial pues la entrada es una sola línea dónde los valores cambian con el tiempo, para esto recibe una señal de un *Timer* que tiene la misma velocidad que el *Timer* que controla al protocolo. Una vez que almacenó la cantidad de valores marcada por un contador, el bloque presenta en su salida un arreglo de valores igual al recibido, ordenados desde el bit menos significativo hasta el más significativo, así podemos disponer de cada valor de aceleración para su manipulación y envío posterior a la interfaz gráfica.

## 3.2.2 Protocolo UART

Como se ha mencionado anteriormente, el proyecto consta de una interfaz gráfica en la cual el usuario puede controlar los movimientos del motor de distintas maneras al mismo tiempo que visualiza una gráfica de posición del motor y otra donde se despliega el valor de la aceleración que registran los sensores ubicados en distintas alturas de la estructura. El protocolo que se usa comúnmente para la comunicación entre la computadora y el FPGA es el UART, que es un protocolo muy sencillo capaz de enviar información binaria entre dos elementos a distintas velocidades configurables de transmisión.

UART (Universal Asynchronous Receiver-Transmitter) es un protocolo digital asíncrono, lo que significa que no requiere de una señal de reloj para transmitir la información, se basa en el cambio de estado de la línea de transmisión para poder comenzar a enviar y recibir datos. Solo cuenta con tres conexiones entre los elementos que se quieren comunicar, el primero es la referencia negativa o tierra (GND), a partir de la cual las otras dos líneas crearán una diferencia de potencial para poder transmitir valores en alto y bajo (binario), las otras dos líneas son de comunicación, una línea para transmitir y otra para recibir información (TX y RX, respectivamente).

El motivo por el cual el protocolo usa dos líneas de transmisión es por la sencillez de la trama, además de que la comunicación se puede hacer en cualquier instante en ambas vías por lo que la transmisión y la recepción pueden chocar si se encentran en la misma línea. El canal de Transmisión y recepción funcionan de la misma manera pero con diferente dirección, la trama se puede observar en la *Figura 20*, ambos tienen un estado de espera que es un valor alto en la línea, el bit de inicio es un valor bajo por lo que el cambio de estado representa el inicio de la transmisión o recepción. Como se mencionó antes, es posible configurar la velocidad de transmisión por lo que el tiempo que dura antes de enviar el siguiente valor se denomina *tiempo bit* y es inversamente proporcional al *Baud Rate*.

Cuando llega el cambio de estado que representa el inicio de la transmisión comienza el tiempo bit, cuando este se cumple la línea presenta el cambio al valor del primer bit, que es el bit menos significativo del byte a enviar, después de cada tiempo bit se envía un nuevo valor hasta completar los 8 bits, posteriormente se envía un bit de paridad. La paridad es una forma de detección de errores, la cual usa los datos enviados para calcular un valor de un bit representativo de la cantidad de valores en alto que se enviaron, esta puede ser par o impar, esto se configura previamente y tienen que coincidir en ambos elementos que se desean comunicar.

Figura 20. Trama del protocolo UART.

La recepción de un valor mediante el protocolo UART lleva una lógica muy sencilla, se necesita que ambos elementos involucrados en la comunicación estén configurados con la misma información: Baud Rate, número de bits y tipo de paridad, con esta información podemos recibir el dato enviado. El sistema de recepción debe estar atento al canal por el que recibe la información (RX), este canal presentará un cambio de estado de alto a bajo cuando la transmisión comience, en ese instante debemos dejar pasar la mitad del tiempo bit, esto permite situarnos a la mitad de un bit en un tiempo específico para poder muestrear el valor y no en una transición donde el valor puede ser incierto (*Figura 21*). El muestreo se hará a partir de ahí cada tiempo bit para obtener todos los valores de la trama, sabemos de antemano cuantos valores se están enviando por lo que detendremos el muestreo cuando obtengamos el número de valores que esperamos para después procesarlos, mientras que el UART regresa al estado inicial de espera para recibir otro byte de información.

Figura 21. Recepción de datos.

La recepción de los datos es de forma serial, por lo que debemos, como en el protocolo anterior, usar un bloque llamado *Registro Serial Paralelo* para convertir el dato en un arreglo en paralelo del tamaño de la información enviada, típicamente 1 byte. El bit de la paridad se deja fuera del arreglo, pues debemos compararlo con un nuevo cálculo de la paridad para el byte recibido, si ambos valores coinciden significa que nuestro valor fue enviado correctamente y podemos hacer uso de el en el sistema, de lo contrario el valor se descarta.

Figura 22. Bloque UART.

El bloque del protocolo UART implementado en la tarjeta de desarrollo FPGA se muestra en la *Figura 22* donde del lado izquierdo se observan las entradas y del derecho las salidas. CLK es la entrada del reloj de la tarjeta y RST es el reset maestro de la tarjeta, esto significa que el bloque funciona cuando la tarjeta está encendida y activa. La entrada STT se activa con un pulso en alto y es la instrucción que necesita para enviar el byte que esté a la entrada DIN que es un arreglo de 8 bits. RXD es el canal por el cual recibirá una trama, mientras que la salida TXD es el canal por el cual enviará la información. La salida EOT envía un pulso en alto cuando finaliza la recepción de un dato y éste se encuentre disponible en la salida DOUT que es un arreglo de 8 bits.

Figura 23. Composición del protocolo UART.

La composición interna del bloque UART se puede observar en la *Figura 23* dónde observamos que en su mayoría está compuesta de bloques genéricos. El *Timer\_0* y el *Timer\_2* deben de tener configurado el valor para cumplir el *Baud Rate*, mientras que el *Timer\_1* tiene configurado la mitad del valor del *Baud Rate*, para poder leer los datos como se explicó anteriormente. El *Multiplexoru\_0* se encarga de enviar los datos con la secuencia correcta y cambia de dato cada que el *FreeCounter\_0* le indica que cambie, éste último bloque tiene configurado la cantidad máxima de cambios que se requieren para enviar por

completo la trama, y se reinicia terminando para estar listo para cuando se requiera enviar de nuevo otro valor.

Como se observa, el protocolo solo es capaz de enviar o recibir un dato de 8 bits por trama, pero es necesario enviar y recibir más datos. Para la transmisión lo único que se requiere es utilizar un multiplexor con la cantidad de datos que se requieren enviar junto a un contador que active el envío de datos y recorra los valores del multiplexor para enviar todos, esto es un arreglo externo al bloque, pues no afecta el uso del UART, más bien lo repite consecutivamente las veces necesarias. En cuanto a la recepción de los datos, lo que se tiene que hacer es utilizar un registro que almacene la cantidad de datos a recibir, y los divida en bytes para poder hacer uso de ellos, ya sabemos que el bloque UART tiene una salida (EOT) que indica cuando un dato ha llegado.

## 3.2.3 Cuadratura del encoder

Dentro de un sistema de *control de lazo cerrado* se encuentra la parte de la instrumentación del actuador que nos permite conocer el estado actual de éste, en el caso particular del proyecto del *Generador de Vibraciones* nuestro actuador es un motor, nuestro control es de posición por lo que la instrumentación debe tener como salida la posición angular del rotor, como se comentó en el *Capítulo III.1.3 El Encoder* conocimos un poco sobre el funcionamiento del encoder incremental, que es el encoder que se usará para este proyecto.

La unidad de control requiere conocer en tiempo real la posición en la que se encuentra el rotor de nuestro BLDCM por lo que tiene la tarea de interpretar las salidas A y B del encoder antes mencionadas. Sabemos que las salidas del encoder están desfasadas 90° con el objetivo de que se pueda diferenciar cuando gira en un sentido o en el otro.

En la *Figura 24* podemos observar gráficamente el comportamiento de las señales en ambas direcciones con el paso del tiempo. Para que la tarjeta pueda interpretar el encoder se diseñó un bloque llamado *QuadratureDecoder* el cual tiene como entradas las señales A y B provenientes del encoder y como salidas tiene un bit de dirección y uno más que indica el cambio de estado. El bloque, internamente, almacena el estado de las entradas en cuatro distintos lapsos de tiempo (Los lapsos que almacena es cuando la entrada ha cambiado), esto permite que el bloque tenga la tabla que se muestra en el lado derecho de la *Figura 24*.

Los estados son almacenados en un arreglo de 4 bits dónde el bit más significativo es el bit más antiguo. Ya que se han almacenado los cuatro estados, el bloque determina la dirección mediante una compuerta XNOR con entradas B[3] y A[2] (En la *Figura 24* se

pueden observar como B<sub>t1</sub> y A<sub>t2</sub>). Cuando el encoder cambia de estado los valores de las tablas se recorren, como se puede notar, cuando gira en dirección de las manecillas del reloj (Clockwise) la salida de la compuerta siempre será un "0", mientras que en el caso contrario (Counter-Clockwise) la salida de la compuerta siempre será un "1".

Figura 24. Secuencia del encoder.

Éste bit de dirección sale del *QuadratureDecoder* hacía un contador bidireccional el cual suma o resta un valor de acuerdo al sentido de giro. El bit que activa el conteo en el contador también sale del *QuadratureDecoder*, éste bit está en alto cada que los valores en las entradas A y B cambian, esto se logra con una compuerta XOR aplicada a los valores B[3], B[2], A[3] y A[2]; lo que se busca es comparar un valor con su consecutivo, siempre que sean diferentes la salida tendrá un "1", pero si son iguales, significa que no cambió o que está cambando de sentido, por lo que a la salida se tendrá un "0". Nótese que cambiará cuatro veces por ciclo, justo esto es la explicación del por qué el conteo del encoder se multiplica por 4.

# 3.2.4 Controlador

El controlador es la parte importante de un servomotor pues este toma el valor deseado y el valor actual de la posición para que a partir de su diferencia se pueda obtener, mediante métodos matemáticos, una señal de corrección de posición que, como ya se mencionó antes, arroja una señal que es transformada en voltaje para mover el motor.

En el *Capítulo III.1.5 Unidad de control* se habló de lo que se conoce como *control proporcional de posición* que, como se dijo, solo utiliza una constante que multiplica al error. En la *Figura 25* podemos observar la forma de la respuesta que podemos esperar. La forma con mayor oscilación representa un control con una *Kp* grande, mientras que la forma más amortiguada representa un control con una *Kp* pequeña. Mientras que la forma que se encuentra entre las dos sería una respuesta ideal para nuestro sistema. Sin embargo, no es posible que dicha forma se pueda conseguir con un controlador sencillo como es el *control proporcional de posición*.

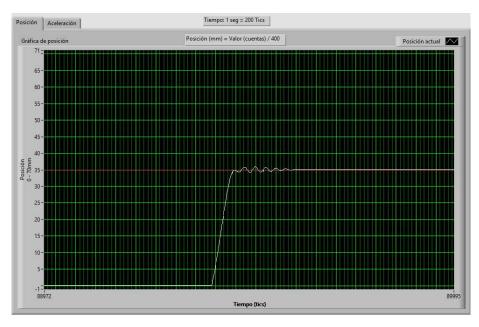

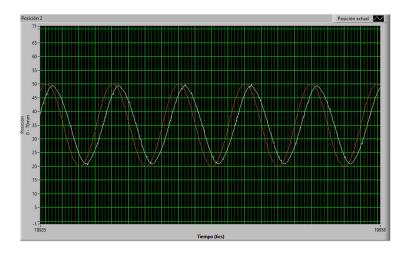

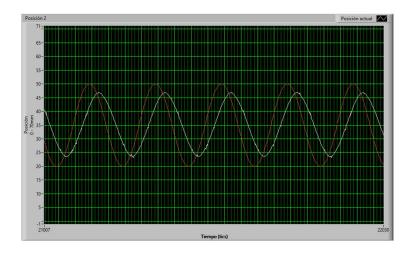

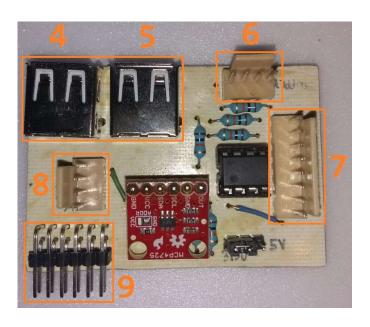

Figura 25. Formas de la posible respuesta transitoria de un control de posición.