#### UNIVERSIDAD AUTÓNOMA DE QUERÉTARO

#### FACULTAD DE INGENIERÍA

### Convertidor CD-CA Monofásico de Puente Completo con FPGA y Síntesis Digital de Señales

#### **Tesis**

Que como parte de los requisitos para obtener el Título de Ingeniero Electromecánico

#### Presenta

Cristian Jonathan Rios Nieves

#### Asesores

Dr. Martín Valtierra Rodríguez

M. en C. Arturo Mejía Barrón

San Juan del Río, Qro. Febrero 2019

# UNIVERSIDAD AUTÓNOMA DE QUERÉTARO FACULTAD DE INGENIERÍA CAMPUS SAN JUAN DEL RÍO

#### CONVERTIDOR CD-CA MONOFÁSICO DE PUENTE COMPLETO CON FPGA Y SÍNTESIS DIGITAL DE SEÑALES

TESIS

Como parte de los requisitos para obtener el título de

INGENIERO ELECTROMECÁNICO

Línea Terminal

MECATRÓNICA

Presenta

CRISTIAN JONATHAN RÍOS NIEVES

Dirigido por:

DR. MARTÍN VALTIERRA RODRÍGUEZ

SINODALES:

DR. MARTÍN VALTIERRA RODRÍGUEZ (11869) Presidente

DR. JESÚS ROONEY RIVERA GUILLÉN (8943) Secretario

M.C. ARTURO MEJÍA BARRÓN (15627) Vocal

DR. MIGUEL TREJO HERNÁNDEZ (6443) Suplente

San Juan del Río, Qro., Noviembre 2018.

#### **RESUMEN**

Día tras día se busca mejorar la tecnología para así poder conseguir mejores resultados en sus aplicaciones, buscando siempre una oportunidad de mejora. En el presente trabajo se elabora la arquitectura digital para poder controlar un inversor monofásico a partir de la síntesis digital de señales, esto gracias al lenguaje en VHDL en conjunto con la tecnología FPGA, incorporando la configurabilidad y en cómputo en paralelo.

Previo al armado del inversor se realizó una simulación en Matlab probando el funcionamiento del SPWM en los dispositivos de potencia. Posterior a esto, se realizó la descripción en VHDL del código para obtener los pulsos de salida de la modulación SPWM a través del FPGA. La tarjeta que se utilizó fue una DE0-nano de la familia Altera.

Con la finalidad de probar el inversor se muestra la aplicación a diferentes cargas tales como iluminarias, fuentes de PC y un motor de CD, así como diferentes condiciones para cada una de ellas, variando la frecuencia y su voltaje de salida. Resultados finales muestran parámetros de operación del inversor así como un prototipo del mismo.

Palabras clave: Inversor monofásico, VHDL, FPGA, Síntesis digital de señales

#### **AGRADECIMIENTOS**

A Dios y a mis Padres por haberme brindado los estudios, por su apoyo, paciencia y amor en cada paso que doy.

A mi hermano por su apoyo y comprensión durante mi formación.

A mis compañeros por cada uno de los momentos que hicieron de esta experiencia algo más agradable día tras día.

A mis profesores por todos los conocimientos que transmitieron, por su paciencia y apoyo.

Se agradece al Programa para el Desarrollo Profesional Docente, para el Tipo Superior (PRODEP), y a la Universidad Autónoma de Querétaro (UAQ) por el financiamiento del material y equipo recibido para el desarrollo de este trabajo de tesis titulado "Convertidor CD-CA monofásico de puente completo con FPGA y síntesis digital de señales" a través de la convocatoria Apoyo a la Incorporación de Nuevos Profesores de Tiempo Completo.

### ÍNDICE

| RESUMEN    | l                                           | ii   |

|------------|---------------------------------------------|------|

| AGRADEC    | IMIENTOS                                    | iii  |

| ÍNDICE     |                                             | v    |

| ÍNDICE DE  | FIGURAS                                     | viii |

| Capítulo 1 |                                             | 1    |

| 1. Introdu | ucción                                      | 1    |

| 1.1. Ante  | ecedentes                                   | 2    |

| 1.2. Des   | cripción del problema                       | 4    |

| 1.3. Just  | ificación                                   | 5    |

| 1.4. Obje  | etivos                                      | 6    |

| 1.4.1.     | Objetivo General                            | 6    |

| 1.4.2.     | Objetivos Particulares                      | 6    |

| 1.5. Plar  | iteamiento General                          | 6    |

| Capítulo 2 |                                             | 9    |

| 2. Funda   | mentación Teórica y Tecnológica             | 10   |

| 2.1. Inve  | rsores                                      | 10   |

| 2.1.1.     | Inversor de medio puente                    | 12   |

| 2.1.2.     | Inversor de puente completo                 | 12   |

| 2.2. M     | odulación Senoidal del Ancho de Pulso       | 13   |

| 2.3. In    | versor SPWM unipolar                        | 14   |

| 2.4. M     | OSFET                                       | 16   |

| 2.5. Pa    | arámetros de operación                      | 17   |

| 2.5.1.     | Factor armónico de enésima componente (HFn) | 17   |

| 2.5.2.     | Distorsión total armónica (THD)             | 17   |

| 2.5.3.     | Factor de distorsión (DF)                   | 18   |

| 2.5.4.     | Armónica de menor orden (LOH)               | 18   |

| 2.6. VI    | HDL                                         | 19   |

| 2.6.1.     | Contador                                    | 19   |

| 2.6.2.     | Timer                                       | 19   |

| 2.6.3.     | Comparador                                  | 19   |

|    | 2.6.    | 4.       | FSM                                                | 20 |

|----|---------|----------|----------------------------------------------------|----|

|    | 2.6.    | 5.       | Active -HDL                                        | 20 |

|    | 2.7.    | FPG      | 9A                                                 | 22 |

|    | 2.7.    | 1.       | Altera Cyclone IV DE0-nano                         | 22 |

|    | 2.8.    | LUT      | -                                                  | 24 |

|    | 2.9.    | Filtr    | o LC                                               | 24 |

|    | 2.10.   | M        | latlab                                             | 25 |

|    | 2.10    | ).1. S   | Simulink                                           | 25 |

| С  | apítulo | 3        |                                                    | 28 |

| 3. | Met     | odolo    | ogía                                               | 29 |

|    | 3.1.    | Mat      | riz de Experimentos                                | 31 |

|    | 3.2.    | Sim      | ulación en Matlab                                  | 33 |

|    | 3.3.    | SPV      | VM en VHDL                                         | 36 |

|    | 3.4.    | Gen      | neración de las LUT con Matlab                     | 37 |

|    | 3.5.    | Pru      | eba del programa en FPGA                           | 41 |

|    | 3.5.    | 1.       | Síntesis del programa                              | 42 |

|    | 3.5.    | 2.       | Visualización de los pulsos en el osciloscopio     | 42 |

|    | 3.5.    | 3.       | Puente de MOSFET                                   | 44 |

|    | 3.5.    | 4.       | Implementación del FPGA con el puente de MOSFET    | 45 |

|    | 3.6.    | Etap     | oa de filtrado (filtro LC)                         | 46 |

|    | 3.6.    | 1.       | Filtro 1                                           | 46 |

|    | 3.6.    | 2.       | Filtro 2                                           | 48 |

| С  | apítulo | <b>4</b> |                                                    | 51 |

| 4. | . Ехр   | erim     | entación y resultados                              | 52 |

|    | 4.1.    | Alim     | nentación de cargas                                | 52 |

|    | 4.1.    | 1.       | Fuente de alto voltaje                             | 52 |

|    | 4.1.    | 2.       | Alimentación de Luminaria Incandescente            | 52 |

|    | 4.1.    | 3.       | Alimentación de Luminaria LED                      | 54 |

|    | 4.1.    | 4.       | Alimentación de una Fuente de PC                   | 56 |

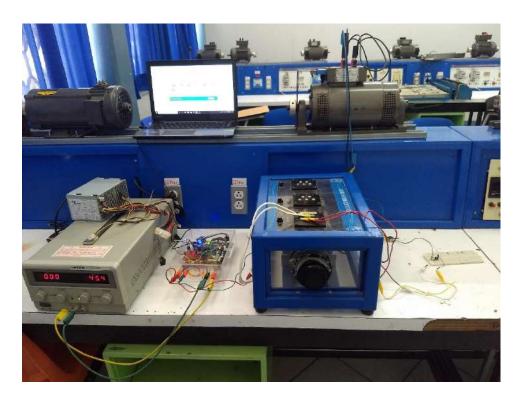

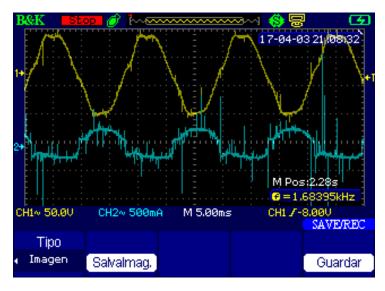

|    | 4.1.    | 5.       | Alimentación de un Motor Eléctrico                 | 57 |

|    | 4.2.    | Obt      | ención de los parámetros de operación del inversor | 59 |

|    | 4.2.    | 1.       | Código en Matlab                                   | 59 |

|    | 4.3.    | Prot     | totipo Final en PCB                                | 65 |

| 5. | Prospectivas | 68 |

|----|--------------|----|

| 6. | Conclusiones | 69 |

| 7. | Referencias  | 71 |

### ÍNDICE DE FIGURAS

| Figura 1 Planteamiento General                                                            | 8    |

|-------------------------------------------------------------------------------------------|------|

| Figura 2 Esquema básico de un inversor                                                    | . 10 |

| Figura 3 Ejemplos de formas de onda a) pulsos cuadrados b) ejemplos de armónicos          | . 11 |

| Figura 4 Inversor en medio puente (Rashid, 1995)                                          | . 12 |

| Figura 5 Inversor en puente completo (Rashid, 1995)                                       | . 13 |

| Figura 6 Formas de onda correspondientes a un inversor SPWM unipolar (Namboodiri,         |      |

| 2014)                                                                                     | . 16 |

| Figura 7 Logo Active- HDL                                                                 | . 20 |

| Figura 8 Vista general del software de Active-VHL                                         | . 21 |

| Figura 9 Ejemplo de simulación en Active-HDL                                              | . 22 |

| Figura 10 Tarjeta DE0-nano                                                                |      |

| Figura 11 Diagrama de un filtro LC con carga donde "L" es el inductor y "C" el capacitor. | 25   |

| Figura 12 Despliegue del menu para abrir Simulink                                         |      |

| Figura 13 Despliegue del menu para abrir Library Browser en Simulink                      |      |

| Figura 14 Metodología                                                                     |      |

| Figura 15 Diagrama general del Inversor.                                                  |      |

| Figura 16 Diagrama a bloques en Simulink del inversor monofásico de puente completo       |      |

| con modulación SPWM                                                                       |      |

| Figura 17 Modulación SPWM en Simulink                                                     |      |

| Figura 18 Salida del inversor en Simulink sin filtrar                                     |      |

| Figura 19 Diagrama a bloques de la estructura digital del SPWM                            |      |

| Figura 20 Señal triangular a muestrear                                                    |      |

| Figura 21 Señal senoidal a muestrear con fase de 0°                                       |      |

| Figura 22 Simulación del programa de modulación SPWM                                      |      |

| Figura 23 Tiempo de desactivación mostrado para los switch Q1 y Q4                        |      |

| Figura 24 Tarjeta ALTERA DE0- Nano Cyclone IV EP4CE22F17C6N                               |      |

| Figura 25 Respuesta de la modulación SPWM para Q1 y Q4                                    |      |

| Figura 26 Visualización del tiempo de retardo presente entre las señales Q1 y Q4          |      |

| Figura 27 Prototipo de tarjeta para inversor                                              |      |

| Figura 28 Salida del inversor medida en AB.                                               |      |

| Figura 29 Respuesta con el filtro 1 (C=0.47uF) con una entrada de 12V                     |      |

| Figura 30 Respuesta con el filtro 1 (C = 0.47uF) para una entrada de 20V                  |      |

| Figura 31 Respuesta con el filtro 1 (C = 0.47uF) para una entrada de 30V                  |      |

| Figura 32 Respuesta con el filtro 2 (C = 20uF y L = 2mH) para una entrada de 12V          |      |

| Figura 33 Respuesta con el filtro 2 (C = 20uF y L = 2mH) para una entrada de 20V          |      |

| Figura 34 Respuesta con el filtro 2 (C = 20uF y L = 2mH) para una entrada de 30V          |      |

| Figura 35 Interconexión para prueba con foco incandescente                                |      |

| Figura 36 Osciloscopio BK PRECISION modelo 2515                                           |      |

| Figura 37 Resultados de la luminaria incandescente obtenidos con el osciloscopio (Seña    |      |

| de voltaje – amarillo y Señal de corriente – cyan).                                       |      |

| Figura 38 Interconexión para prueba con foco de LED                                       |      |

| Figura 39 Resultados de la luminaria LED obtenidos con el osciloscopio (Señal de volta    |      |

| – amarillo y Señal de corriente – cyan)                                                   | . 55 |

| Figura 40 Interconexión para prueba con fuente de PC                                | 56   |

|-------------------------------------------------------------------------------------|------|

| Figura 41 Resultados de la fuente de PC obtenidos con el osciloscopio (Señal de vol | taje |

| – amarillo y Señal de corriente – cyan)                                             | 57   |

| Figura 42 Interconexión para prueba con motor eléctrico de DC                       | 58   |

| Figura 43 Resultados del motor de CD obtenidos con el osciloscopio (Señal de voltaj | e –  |

| amarillo y Señal de corriente – cyan)                                               | 58   |

| Figura 44 Señal de voltaje de Foco a 60 V @ 60 Hz                                   | 60   |

| Figura 45 Señal de voltaje de Foco a 80 V @ 30 Hz                                   | 62   |

| Figura 46 Forma de onda de corriente de Motor a 80 V @ 30 Hz                        | 64   |

| Figura 47 Forma de onda de corriente de Foco a 80 V @ 60 Hz                         | 65   |

| Figura 48 PCB #1 con las señales digitales y drivers                                | 66   |

| Figura 49 PCB #2 con puente de MOSFET y entradas CD y salidas CA                    | 67   |

| Figura 50 Prototipo final del inversor                                              | 67   |

|                                                                                     |      |

# Capítulo 1

Introducción

#### 1. Introducción

Un inversor es aquel que convierte energía de CD (corriente directa) a CA (corriente alterna), dicha conversión puede ser con valores de frecuencia y magnitud fijos o variables. En general los inversores son utilizados en la industria de diversas formas; ejemplo, en motores como variadores de frecuencia a fin de regular la velocidad, en energías alternas para poder integrarlas a las líneas de alimentación comerciales, en alimentaciones ininterrumpibles de potencias, entre otros.

Los inversores pueden presentar diferentes configuraciones para su aplicación, por ejemplo para variar la salida del inversor puede darse por la variación del voltaje de entrada o por la variación de la ganancia del inversor (generalmente por medio de la modulación del ancho de pulso: *Pulse Width Modulation, PWM*), según sea el caso. La relación entre el voltaje de salida en CA y el voltaje de entrada en CD nos da la ganancia del inversor.

Los inversores ideales suponen una salida puramente senoidal, aunque los inversores reales no lo entregan. Es muy común encontrar en aplicaciones de baja potencia inversores con pulsos cuadrados y grandes cantidades de armónicos; casos que no son vistos en aplicaciones de alta potencia. Para estos últimos casos son muy útiles los semiconductores de alta velocidad que permiten disminuir los armónicos mediante las técnicas de conmutación, dando como resultado inversores con un nivel bajo de distorsión a la salida. La fuente de entrada de un inversor puede ser una batería, una celda solar o cualquier otra fuente de CD.

Para realizar la modulación es común utilizar osciladores para poder generar las señales senoidales y triangulares en modulaciones SPWM (*Sinusoidal Pulse Width Modulation*), estos osciladores son susceptibles a cambios de temperatura, humedad, etc., lo cual se ve reflejado en su comportamiento. Una solución a esto es trabajar con síntesis digital de señales por medio de LUT (*Look Up Table*), estas últimas son tablas de consulta las cuales guardan información para poder realizar la comparación de las señales senoidales y triangulares necesarias para la modulación SPWM. Aplicando la síntesis digital de señales en un FPGA (*Field Programmable Gate Array*) es posible mandar los pulsos necesarios para activar los dispositivos de activación y desactivación controlada (MOSFET por ejemplo) de manera eficiente gracias a la velocidad y paralelismo de procesamiento del FPGA, dando así una mejor calidad al inversor a partir de la técnica de modulación.

#### 1.1. Antecedentes

En la Universidad Autónoma de Querétaro se han realizado trabajos referentes al uso de inversores. En la tesis de Aguilar (2011) se presentó un inversor trifásico con modulación SPWM con aplicación a motores trifásicos. Para generar las señales para el SPWM se utilizó el algoritmo CORDIC. Se utilizaron IGBT para la generación de los pulsos. Se realizó también la parte de generación de señales (Amézquita Sánchez Juan Pablo, 2012), en este trabajo se hace mención a la parte de la generación de señales de forma digital. Como se explica en ese trabajo, las técnicas para la generación de señales se basaban en circuitos osciladores a base de transistores, pero eran susceptibles a cambios de temperatura, humedad, presión, potencial de alimentación y a cargas eléctricas. Los cambios que se presentan se reflejan en la forma de la onda, amplitud y frecuencia, lo cual arroja como resultado una señal de indeseable. Esto puede ser evitado al sintetizar una señal de forma digital, esto ayuda a la calidad de la señal y permite controlar la señal en frecuencia, amplitud y el factor de modulación. A diferencia de los trabajos antes mencionados, la propuesta presentada en este trabajo pretende aprovechar las ventajas de la tecnología FPGA y síntesis digital de señales para su reconfigurabilidad, a través de la reconfigurabilidad del FPGA se puede variar la frecuencia sin la necesidad de modificar o sustituir algún componente electrónico, todo esto se realizaría en software. Además, se dejan las estructuras digitales independientes de fabricante, es decir no se usan arquitecturas de fabricantes o con alguna propiedad intelectual.

En el Centro Nacional de Investigación y Desarrollo Tecnológico se desarrolló el trabajo para el análisis de estrategias de puesta en paralelo de convertidores CD-CA (Mendoza, 2005), en este trabajo se especifican datos de diseño de los inversores, así como de la modulación SPWM, evidenciando los beneficios que menciona para un filtro LC en paralelo. Además, se mencionan también las importancias de los tiempos de retardo que se deben presentar en las señales activación y desactivación de los tiristores.

Luna et al. presentan el trabajo de diseño didáctico de convertidores CD-CA. En este documento presentan la elaboración física del SPWM y los resultados son favorables. Se retoma la parte de utilizar un filtro LC en paralelo para el filtrado de la señal; no obstante, la generación de señales es completamente analógica, ejemplo: usando amplificadores operacionales.

También hay antecedentes en los cuales no se ocupan la tecnología FPGA como base de procesamiento. Por ejemplo, hay casos en los que se utilizan microcontroladores (Alejandro, et. al.) y tarjetas de desarrollo basadas en microcontrolador como las de la familia Arduino (Andriach, et. al., 2013). En este último trabajo se hace referencia a las limitantes o consideraciones a tener en cuenta cuando se trabaja en la plataforma de Arduino. Otro caso en el cual se utiliza Arduino, es el trabajo presentado por Herrera (2017) solo que en este caso se agrega un variador de velocidad para permitir un arranque suave en aplicaciones a motores. El uso de tecnologías programables permite incrementar la flexibilidad en su uso, por ejemplo, en el variador de velocidad se genera un perfil de frecuencia variable lo cual no podría hacerse, o al menos de una forma sencilla, usando puramente electrónica analógica.

También se han presentado casos en los cuales se ha utilizado Arduino pero los pulsos son generados en Matlab, es decir, Arduino solo es el intermediario; es decir, tarjeta Arduino recibe desde Matlab la información y esta los manda hacia los MOSFET/IGBT. En el trabajo de Chandra et. al. se realiza un trabajo similar en concepto para un inversor trifásico. En el trabajo de Pereira, Colombia (Ballesteros, 2008), se realizó un trabajo de modulación PWM en FPGA basado en máquinas de estados, en el cual se muestran algunas mejoras para optimizar los recursos mediante la simplificación de las máquinas de estados. Adicional a esto, en Universiti Malaysia Perlis (Isa et. al., 2007), se elaboró una modulación SPW M en Altera Max Plus II con el cual concluyen, gracias a sus herramientas de simulación, las mejoras y ventajas al realizar en FPGA la modulación ya que otorga un mejor control y es más sencillo poder modificar los valores de frecuencia y amplitud sin generar cambios al programa como tal; además de que, gracias a las simulaciones previas, es más viable pasar a la implementación en un FPGA físico. Una publicación del International Journal for Innovative Research in Science & Technology, IJIRST, (Anuja Namboodiri et al., 2014) muestra una simulación realizada en Matlab para poder realizar el SPWM, la cual se retoma considerando los mismos parámetros a fin de corroborar los resultados obtenidos. Un trabajo realizado con una tarjeta Altera DE2 para generar las señales de activación para IGBT es también presentado en la literatura; en este caso, se muestra el SPWM de forma bipolar, aunque también hace uso de tablas de consulta para el procesamiento del FPGA, las cuales son generadas mediante Matlab (Abu, et. al., 2009).

Aunque en la literatura revisada ya hay trabajos que presentan arquitecturas basadas en FPGA enfocadas en inversores, aún hay puntos a desarrollar; por ejemplo,

hacer uso de metaprogramación para generar código y mejorar la parte del diseño digital, también la integración de código para la comunicación entre el FPGA y la PC con el objetivo de configurar parámetros de operación como amplitud y frecuencia. Además, el desarrollo de este proyecto sentará un antecedente dentro de la institución que de soporte a futuros desarrollos más complejos.

#### 1.2. Descripción del problema

Actualmente existe un gran número de aplicaciones que requieren del uso de inversores. Aunque en términos generales, el concepto de inversor no varía de aplicación a aplicación, lo que si varía son sus parámetros de configuración y operación; por ejemplo, puede variar su frecuencia y su amplitud, así como el voltaje de entrada. En este sentido, un inversor que pueda atender un gran número de aplicaciones es de al alto valor agregado; no obstante, esta tarea no es sencilla ya que diferentes aspectos deben ser tomados en cuenta. Entre estos aspectos, el cambio de frecuencia es de los más importantes. Aunque existen equipos comerciales que permiten generar un gran número de frecuencias, su costo es elevado debido precisamente a esta funcionalidad; es decir, un inversor que puede generar una sola frecuencia es mucho más barato que uno que puede generar muchas. Sin embargo, la ventaja de tener esta capacidad pasa a segundo término cuando el usuario no requiere de todas esas funcionalidades, convirtiéndose en una mala opción costo beneficio. Pero, por otro lado, para los fabricantes no es rentable hacer inversores que solo puedan con una frecuencia ya que dependerían exclusivamente de usuarios particulares. En este sentido, el tener una plataforma base y genérica en la que solo cambiando el software se pueda configurar los requerimientos especiales y exactos para cada aplicación llega a ser una prestación atractiva para los usuarios ya que, en palabras sencillas, estaría pagando solo por lo que requiere. Este ejemplo de frecuencia, aplica similarmente para los otros parámetros/variables involucradas en la operación del inversor.

A pesar del optimismo puesto en la necesidad anterior, el lograr hacer ese dispositivo con todas las prestaciones de configurabilidad no es tarea sencilla. Desde el punto de vista diseño digital se deben construir estructuras que puedan ser reconfigurables, se deben establecer estructuras de comunicación que permitan la configurabilidad ya sea por PC u otro medio que el usuario pudiera requerir. También, aspectos de memoria, tiempos de ejecución, robustez, etc., son aspectos que se deben cuidar cuando se busca la generalidad del sistema. Por otro lado, también se debe buscar la independencia de

usuarios expertos para la configurabilidad del sistema, ya que usuarios con poca o nula experiencia deben familiarizarse rápidamente con el sistema y no tener que ser expertos en diseño digital (por mencionar un ejemplo) para poder entrar a la arquitectura digital y hacer las modificaciones necesarias.

Por lo tanto, aunque el desarrollo del sistema con las prestaciones anteriormente mencionadas, es un gran reto, es deseable comenzar a establecer el sistema o prototipo base que pueda servir como punto de partida.

#### 1.3. Justificación

La síntesis digital de señales se propone como una solución para poder eliminar la electrónica analógica y así mejorar la flexibilidad en el manejo y configuración de los inversores. Gracias a ello es posible asemejar la salida del inversor a la señal deseada tanto en forma y frecuencia. Además la programación en VHDL, gracias a su arquitectura abierta, permitirá la reconfiguración de manera más rápida y con la flexibilidad para acoplarse a cualquier tipo de necesidad. Esto último quiere decir que puede ser de uso académico o industrial.

El procesamiento digital de las señales permite obtener siempre los mismos resultados en la modulación SPWM, de tal manera que el comportamiento del inversor será de forma constante, independientemente a las condiciones en las cuales se encuentre trabajando, dado que ni las interferencias de temperatura y de estática dañarán o afectarán en el funcionamiento del inversor, esto en términos relativos a los generadores de señales basados en amplificadores operacionales.

También, la disminución en costo es un aspecto importante, ya que la fabricación no es tan elevada en términos de reproducción ya que las estructuras son totalmente portables y la calidad y eficiencia son aceptables considerando aspectos y características de tecnologías analógicas vs digitales, reduciendo el costo sin afectar la calidad. Aunque el proyecto se orienta a un inversor monofásico las estructuras desarrolladas pueden ser modificadas y expandibles (reúso) a un inversor trifásico/polifásico. Además, la manipulación de parámetros de ganancia y frecuencia puede ser configurada y programada de manera constante y variable en el tiempo, ejemplo un perfil de frecuencia para un variador de velocidad.

Por último, el uso de tecnologías FPGA con sus ventajas inherentes sobre otras tecnologías permitirá el cómputo en paralelo, la configurabilidad y la expansión de estructuras digitales para otro tipo de tareas. También la integración futura de otros módulos para diversas aplicaciones, ejemplo control inalámbrico.

#### 1.4. Objetivos

#### 1.4.1. Objetivo General

Diseñar y desarrollar un convertidor de CD a CA monofásico de puente completo controlado con FPGA y síntesis digital de señales para alimentación de cargas eléctricas en CA a diferentes frecuencias.

#### 1.4.2. Objetivos Particulares

- 1. Construir y simular el inversor de puente completo en SIMULINK Matlab.

- Construir una topología para inversor de puente completo usando interruptores de tipo MOSFET.

- 3. Generar las estructuras digitales de síntesis de señal en FPGA para ondas senoidales y triangulares.

- 4. Desarrollar el módulo de control Unipolar en FPGA para el inversor de puente completo.

- 5. Integrar y validar el inversor desarrollado usando distintos niveles de CD y distintos parámetros de ajuste del SPWM.

- 6. Probar el inversor con dos distintas cargas eléctricas en AC, una luminaria y un motor.

#### 1.5. Planteamiento General

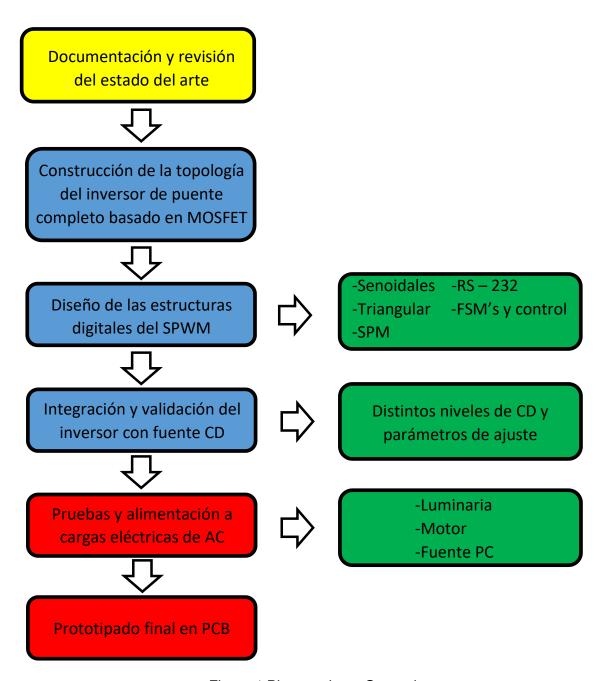

El trabajo se dividirá en diferentes partes a fin de marcar los pasos a seguir para poder obtener el producto final.

En la figura 1 se puede apreciar que la primera parte que se debe de hacer es buscar referencias de trabajos que se hayan realizado anteriormente para poder conocer su desempeño y a partir de ello poder usar la información obtenida como base y oportunidad de mejora. La siguiente fase es poder construir la topología del inversor en puente completo basado en MOSFET, estos serán utilizados en pruebas iniciales, tomando en cuenta que son económicos y pueden ser útiles en caso de tener complicaciones con la parte programable (tiempos).

Teniendo este modelo se puede trabajar sobre la parte lógica programable que se utilizará para la activación de los circuitos, recordando que se requieren de señales digitales para la activación y desactivación de los interruptores del circuito. Además se debe agregar la parte de la máquina de control de estados (*finite state machine*, FSM) que sean necesarias para poder unir todos los elementos que van a aportar para la generación de los pulsos de activación. Para la parte de síntesis de señales senoidales y triangulares se desarrollará una interfaz gráfica de usuario (GUI, *graphic interface user*) en Matlab para mejorar el desempeño en el proceso de la generación de formas de onda. A partir de ello se podrá empezar a trabajar con las fuentes de CD y diferentes valores en los parámetros de funcionamiento del inversor, ejemplo, la frecuencia.

Posteriormente se comenzarán las pruebas con cargas para poder ver su capacidad de alimentación y desempeño ante distintos niveles de carga (contenido armónico y potencia).

Como parte final se realizará el prototipo en PCB y accesorios como parte de la entrega final del inversor.

Figura 1 Planteamiento General.

## Capítulo 2

Fundamentación Teórica y Tecnológica.

#### 2. Fundamentación Teórica y Tecnológica.

#### 2.1. Inversores

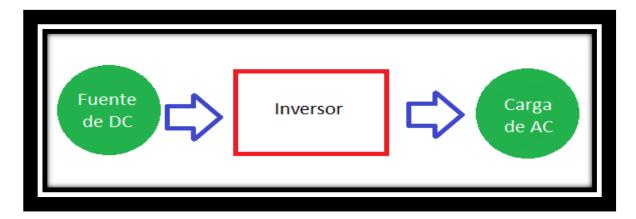

Los convertidores de CD a CA se conocen como inversores (Inversor, 2018). La función de un inversor es cambiar un voltaje de entrada en CD a un voltaje simétrico de salida en CA, es decir que tanto en la parte positiva como en la negativa o a partir de valor medio sean iguales. Un esquema básico de esto se muestra en la figura 2. Tanto el voltaje de salida como la frecuencia pueden ser fijos o variables. En general, se pueden presentar algunas condiciones de operación dependiendo del voltaje de entrada y de un factor llamado ganancia del inversor; por ejemplo, si se modifica el voltaje de la entrada de CD y la ganancia del inversor se mantiene constante, es posible obtener un voltaje variable a la salida. Por otra parte, si el voltaje de entrada en CD es fijo y no es controlable, se puede obtener un voltaje de salida variable si se varía la ganancia del inversor, esto por lo general se hace controlando la modulación dentro del inversor. La ganancia del inversor se puede definir como la relación entre el voltaje de salida en CA y el voltaje de entrada en CD.

Figura 2 Esquema básico de un inversor.

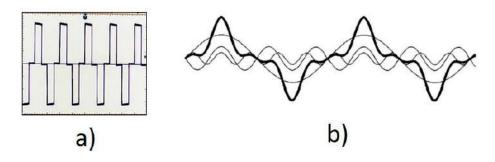

De forma ideal, las formas de onda de voltaje de salida en un inversor deben ser senoidales. Sin embargo, en los inversores reales no son senoidales y contienen ciertas armónicas, en la figura 3 se muestran ejemplos de estas formas de onda. Los armónicos son componentes senoidales con frecuencias múltiplos de la fundamental; por ejemplo, si la componente fundamental es de 60 Hz, las componentes frecuenciales del segundo y

tercer armónico serán 120 y 180 Hz, respectivamente. Se sabe que una señal de cualquier forma de onda puede ser representada por una sumatoria de señales senoidales de acuerdo a las series de Fourier (Fourier, 2018), en este sentido, una señal cuadrada tiene un gran contenido armónico al requerir de una gran cantidad de señales senoidales para su representación. Pero por otro lado, dada la disponibilidad de los dispositivos semiconductores de potencia de alta velocidad, es posible minimizar o reducir significativamente el contenido armónico del voltaje de salida mediante las técnicas de conmutación.

Figura 3 Ejemplos de formas de onda a) pulsos cuadrados b) ejemplos de armónicos.

El uso de las inversores es muy común en aplicaciones industriales tales como la propulsión de motores de CA de velocidad variable, la calefacción por inducción, las fuentes de respaldo y las de poder, alimentaciones ininterrumpibles de potencia, balastros para iluminación, etc. En estas aplicaciones y considerando la figura 2, la entrada puede ser una batería, una celda de combustible, una celda solar u otra fuente de CD. Por otro lado, como se comentó, los inversores pueden ser monofásicos o trifásicos; en este sentido, las salidas monofásicas típicas son (1) 120 V a 60 Hz, (2) 220 V a 50 Hz y (3) 115 V a 400 Hz. Para sistemas trifásicos las salidas típicas son (Gallino Cardona et al., 2009): (1) 220/380 V a 50 Hz, (2) 120/208 V a 60 Hz y (3) 115/200 V a 400 Hz.

Los inversores se pueden clasificar básicamente en dos tipos: (1) inversores monofásicos y (2) inversores trifásicos. Cada tipo puede utilizar dispositivos con activación y desactivación controlada (es decir BJT, MOSFET, IGBT, MCT, SIT, FTO) o tiristores de conmutación forzada, según la aplicación. Estos inversores utilizan por lo general señales de control PWM para producir un voltaje de salida en CA. Un inversor se llama inversor alimentado por voltaje (VFI) si el voltaje de entrada se conserva constante, inversor

alimentado por corriente (CFI) si la corriente de entrada se conserva constante e inversor enlazado en CD variable si el voltaje de entrada es controlable.

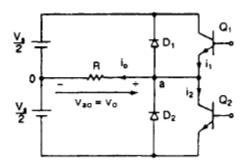

#### 2.1.1. Inversor de medio puente

El circuito inversor está formado por dos pulsadores, figura 4. Cuando sólo el transistor Q1 está activo durante el tiempo  $T_0/2$ , el voltaje instantáneo a través de la carga  $v_0$  es  $V_s/2$ . Si sólo el transistor Q2 está activo durante un  $T_0/2$ , aparece el voltaje  $-V_s/2$  a través de la carga. El circuito lógico debe diseñarse de tal forma que Q1 y Q2 no estén activos simultáneamente.

Este inversor requiere una fuente de CD de tres conductores, cuando un transistor está inactivo, su voltaje inverso es *Vs* en lugar de *Vs*/2.

Figura 4 Inversor en medio puente (Rashid, 1995).

El voltaje rms (*root mean square*, raíz media cuadrática) de salida se puede encontrar a partir de

$$V_0 = \left(\frac{2}{T_0} \int_0^{\frac{T_0}{2}} \frac{V_s^2}{4} dt\right)^{1/2} = \frac{V_s}{2} \tag{1}$$

#### 2.1.2. Inversor de puente completo

Está formado por cuatro pulsadores, tal como se ve en la figura 5. Cuando los transistores Q1 y Q3 se activan simultáneamente, el voltaje de entrada  $V_s$  aparece a través de la carga. Si los transistores Q2 y Q4 se activan al mismo tiempo, el voltaje a través de la carga se invierte y adquiere el valor de  $-V_s$ .

Figura 5 Inversor en puente completo (Rashid, 1995).

El voltaje rms de salida se puede determinar a partir de

$$V_0 = \left(\frac{2}{T_0} \int_0^{\frac{T_0}{2}} V_S^2 dt\right)^{\frac{1}{2}} = V_S \tag{2}$$

#### 2.2. Modulación Senoidal del Ancho de Pulso

En muchas aplicaciones industriales a menudo es necesario controlar el voltaje de salida de los inversores para (1) hacer frente a las variaciones de entrada de CD, (2) para la regulación del voltaje de los inversores y (3) para los requisitos de control constante en voltaje y la frecuencia. Existen varias técnicas para modificar la ganancia del inversor. El método más eficiente de controlar la ganancia (y el voltaje de salida) es incorporar en los inversores el control de modulación del ancho de pulso (PWM).

El ancho de cada pulso varía en proporción a la amplitud de una onda senoidal evaluada en el centro del mismo pulso. El factor de distorsión y las armónicas de menor orden se reducen en forma significativa. Las señales de compuerta se generan al comparar una señal senoidal de referencia con una onda portadora triangular de frecuencia  $f_c$ . Este tipo de modulación se utiliza por lo común en las aplicaciones industriales; se abrevia SPWM. La frecuencia de la señal de referencia,  $f_r$ , determina la frecuencia de la salida del

inversor,  $f_o$ , y su amplitud pico,  $A_r$ , controla el índice de modulación, M, y en consecuencia, el voltaje rms de salida,  $V_o$ . El número de pulsos por medio ciclo depende de la frecuencia portadora. Dentro de la restricción de que los transistores en el mismo brazo no pueden conducir simultáneamente.

El voltaje rms de salida puede controlarse si se varía el índice de modulación *M*. Es fácil observar que el área de cada pulso corresponde aproximadamente al área bajo la onda senoidal entre los puntos adyacentes de los periodos inactivos de las señales de excitación.

El índice de modulación esta dado de la siguiente manera:

$$M = \frac{A_m}{A_p} \tag{3}$$

donde *Am* y *Ap* representan las amplitudes de las señales moduladora y portadora, respectivamente.

La señal triangular es la señal portadora la cual tiene amplitud y frecuencia fijas, mientras que la señal senoidal, señal moduladora, tiene frecuencia y amplitud variable.

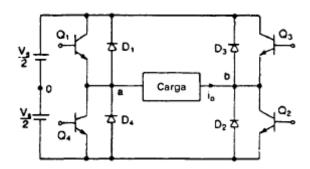

#### 2.3. Inversor SPWM unipolar

La modulación unipolar normalmente requiere de dos señales senoidales moduladoras  $V_m$  y  $V_{m^-}$  las cuales son de la misma magnitud y frecuencia pero con un ángulo de desfase de 180°. Las dos señales de modulación son comparadas con una señal triangular portadora común  $V_{cr}$  generando dos señales de compuerta  $v_{g1}$  y  $v_{g3}$  para los dos switches superiores Q1 y Q3 (figura 5). Los voltajes de salida de las compuertas del inversor cualesquiera que estas sean serán entre cero y  $+V_d$  durante el medio ciclo positivo o serán entre cero y  $-V_d$  durante el medio ciclo negativo de la frecuencia de la señal fundamental, de aquí que se llame modulación unipolar. El inversor de conmutación unipolar ofrece una reducida perdida en la conmutación y genera menos EMI (*ElectroMagnetic Interference*). Por razones de eficiencia y contenido armónico, el inversor de conmutación unipolar tiene la ventaja.

La sobremodulación se presenta cuando el índice de modulación es mayor que la unidad. Esto causa una reducción en el número de pulsos en la forma de onda del voltaje

de línea a línea dando así lugar a que surjan armónicos de bajo orden. Además los anchos de pulso en el centro del medio ciclo negativo y del medio ciclo positivo tenderían a desaparecer.

El orden de encendido-apagado se presenta de la siguiente forma, considerando la Figura 5:

- Q1 → Vcontrol > Vtri

- Q4 → Vcontrol < Vtri</li>

- Q2 → -Vcontrol < Vtri

- Q3 → -Vcontrol > Vtri

Las formas de onda correspondientes a este tipo de modulación se pueden apreciar en la figura 6, siendo en la parte superior las señales tanto moduladores como la portadora, en la segunda parte se muestran los pulsos de compuerta generados con la comparación de las señales, siendo  $v_{g1}$  el resultado de la comparación de la señal portadora con la señal senoidal con ángulo de fase igual a 0°, y  $v_{g3}$  como resultado de comparar la señal portadora con la señal senoidal con ángulo de fase igual a 180°. La siguiente gráfica en la imagen muestra las señales de salida de los nodos del puente del inversor; por último se muestra la señal de salida del inversor sin filtro (pulsos cuadrados) y la señal con filtro a la salida (senoidal).

Figura 6 Formas de onda correspondientes a un inversor SPWM unipolar (Namboodiri, 2014).

#### 2.4. MOSFET

Un MOSFET de potencia es un dispositivo controlado por voltaje, el cual requiere sólo de una pequeña corriente de entrada. La velocidad de conmutación es muy alta siendo los tiempos de conmutación en el rango de los nanosegundos. Los MOSFET de potencia están encontrando cada vez más aplicaciones en los convertidores de alta frecuencia y baja potencia. Los MOSFET no tienen los problemas de los fenómenos de ruptura secundaria que tienen los BJT. Sin embargo, los MOSFET tienen problemas de descargas electrostáticas, por lo que su manejo requiere de cuidados especiales. Además es relativamente difícil protegerlos bajo condiciones de falla por cortocircuito.

#### 2.4.1. MOSFET IRF640

El MOSFET es seleccionado como el conmutador a utilizar en el presente trabajo gracias a su rápido switcheo, baja resistencia y además la rentabilidad que ofrece en cuanto a costo se refiere, claro sin dejar de lado los requerimientos para el buen funcionamiento

del inversor (nivel de voltaje y corriente adecuados). Los tiempos de retraso de encendido y apagado de este dispositivo son de 14 y 45 nanosegundos respectivamente, agregando a estos el tiempo de carga y descarga del MOSFET de 51 y 36 nanosegundos respectivamente.

Una ventaja más del uso de estos componentes es su practico cicuito de funcionamiento.

#### 2.5. Parámetros de operación

La salida de los inversores reales contiene armónicas. La calidad de un inversor por lo general se evalúa en términos de los siguientes parámetros de rendimiento (Inversor, 2018).

#### 2.5.1. Factor armónico de enésima componente $(HF_n)$

El factor armónico (correspondiente a la enésima armónica) es una medida de la contribución armónica individual y se define como

$$HF_n = \frac{V_n}{V_1} \tag{4}$$

Donde  $V_1$  esel valor rms de la componente fundamental y  $V_n$  es el valor rms de la enésima componente armónica.

#### 2.5.2. Distorsión total armónica (THD)

La distorsión armónica total es una medida de la similitud entre la forma de onda y su componente fundamental, se define como:

$$THD = \frac{1}{V_1} \left( \sum_{n=2,3...}^{\chi} V_n^2 \right)^{\frac{1}{2}}$$

(5)

Donde las variables son igual que en la ecuación (4) y x representa el número máximo de componentes armónicas, típicamente 40 o 50 según normativa.

#### 2.5.3. Factor de distorsión (DF)

El valor THD proporciona el contenido armónico total, pero no indica el nivel de cada uno de los componentes. Si en la salida de los inversores se utiliza un filtro, las armónicas de orden más alto se atenuaran con mayor eficacia. Por lo tanto, resulta importante conocer tanto la frecuencia como la magnitud de cada componente. El factor de distorsión indica la cantidad de distorsión armónica que queda en una forma de onda particular después de que las armónicas de esa forma hayan sido sujetas a una atenuación de segundo orden (es decir divididas por  $n^2$ ). Por lo tanto, el valor de DF es una medida de la eficacia en la reducción de las componentes armónicas no deseadas, sin necesidad de especificar valores de un filtro de carga de segundo orden y se define como:

$$DF = \frac{1}{V_1} \left[ \sum_{n=2,3...}^{\chi} \left( \frac{V_n}{n^2} \right)^2 \right]^{\frac{1}{2}}$$

(6)

El factor de distorsión de una componente armónica individual (o de orden *n*) se define como

$$DF_n = \frac{V_n}{V_1 n^2} \tag{7}$$

#### 2.5.4. Armónica de menor orden (LOH)

La armónica de menor orden es aquella componente cuya frecuencia es más cercana a la fundamental, y cuya amplitud es mayor o igual al 3% de la componente fundamental.

#### 2.6. VHDL

VHDL es el acrónimo que representa la combinación de VHSIC y HDL, donde VHSIC es el acrónimo de *Very High Speed Integrated Circuit* y HDL es a su vez el acrónimo de *Hardware Description Language*.

Existen diversos lenguajes descriptivos que han sido desarrollados en los últimos años, pero el lenguaje que más difusión ha tenido y que se utiliza mayormente es VHDL.

Las características principales que hacen del VHDL el lenguaje universal de descripción de circuitos son el ser un lenguaje estándar definido como tal por el IEEE y que los proveedores del paquete tienen que seguir el estándar, haciendo que los diseños sean portátiles a cualquier plataforma. En lo siguiente se definen algunas estructuras digitales básicas y necesarias para el desarrollo de este proyecto.

#### 2.6.1. Contador

Los contadores permiten dar una secuencia preestablecida, con la condición de ser consecutiva (Troncoso, 2007). Un contador puede ir en dirección creciente o decreciente según sea la necesidad.

Un contador puede además contener diferentes características, pude ser de carrera libre o puede tener señales que lo condiciones a seguir contando, puede depender de una señal de habilitación, el número de conteo puede ser fijo o puede ser variable.

#### 2.6.2. Timer

Un timer o temporizador es una variación del contador, siendo una herramienta utilizada para permitir que alguna función se realice cada determinado tiempo. En aplicaciones en VHDL es muy útil para mandar señales que determinan tiempos de retardo.

#### 2.6.3. Comparador

Un comparador realiza la prueba entre dos palabras binarias del mismo formato y código, y determina si el resultado es mayor, menor o igual (Troncoso, 2007), derivando en diferentes acciones o diferentes funciones; de tal manera que un comparador se vuelve una pieza importante en la programación. Una función de comparación permite realizar la

operación el número de veces necesarias sin necesidad de gastar muchos recursos del FPGA.

#### 2.6.4. FSM

Una FSM o máquina de estados es un conjunto de estados que sirve de intermediario para la relación entre las entradas y salidas que definen la salida correspondiente para el estado actual. En la máquina de estados se deben de considerar lo siguiente: estados, transiciones, entradas y salidas (Troncoso, 2007).

#### 2.6.5. Active -HDL

Figura 7 Logo Active- HDL.

Active – HDL es un software utilizado para describir y simular códigos en VHDL (logo en figura 7). Gracias a la simulación que permite hacer se puede localizar algún error y al mismo tiempo tener un mejor panorama de lo que se está haciendo.

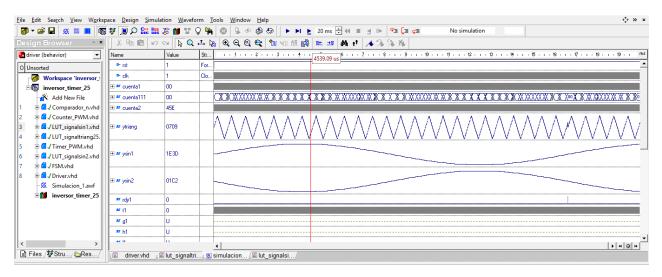

El ambiente de trabajo es relativamente amigable, permitiendo ver el proyecto de una forma fácil y sencilla. En la parte de la izquierda, como se muestra en la figura 8, se despliega el listado de archivos del proyecto, así como las simulaciones que se han realizado. También se tiene el área de consola en la parte inferior, aquí se muestran todos los comandos o acciones que hace el programa. Dentro de esta parte es donde se indican o describen los errores generados para poder ser ubicados y dar solución en caso de que haya alguno.

Figura 8 Vista general del software de Active-VHL.

Las simulaciones se pueden configurar para que corran o se ejecuten por un tiempo determinado, incluyendo el comportamiento de las distintas entradas a lo largo de diferentes ciclos de reloj. Los gráficos generados debido al cambio de variables, entradas y salidas ayudan a visualizar el correcto desempeño de la arquitectura digital así como a detectar errores de ejecución antes de cargar el programa al FPGA y así evitar daños a este mismo. Un ejemplo de una simulación se muestra en la figura 9.

Figura 9 Ejemplo de simulación en Active-HDL.

#### 2.7. FPGA

Dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionabilidad puede ser configurada mediante un lenguaje de programación especializado. Su lógica programable puede ser tan sencilla como las compuertas lógicas hasta complejos sistemas en un chip. Estos proporcionan alta velocidad, reprogramación y costos menores.

#### 2.7.1. Altera Cyclone IV DE0-nano

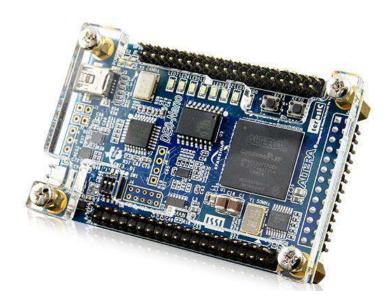

Figura 10 Tarjeta DE0-nano.

La tarjeta DE0-nano (ver figura 11) presenta una plataforma de desarrollo FPGA de tamaño compacto adecuado para una amplia gama de proyectos de diseño de portátiles, tales como robots y proyectos móviles.

A continuación, se muestra una tabla con las especificaciones básicas de la tarjeta DE0-nano. Con esta tabla se puede ver lo versátil que es esta tarjeta para diferentes tipos de aplicaciones.

Tabla 1 Tabla de especificaciones de tarjeta DE0-nano

| Altera Cyclone DE0-nano   |                            |  |

|---------------------------|----------------------------|--|

| Elementos analógicos      | 22.320                     |  |

| SDRAM                     | 32 MB                      |  |

| EEPROM                    | 2 kb                       |  |

| Memoria de configuración  | 64 MB                      |  |

| Canales de conversión A/D | 8 de 12 bits               |  |

| Acelerómetro              | Si, 3 ejes                 |  |

| Alimentación              | USB o alimentación externa |  |

| Pulsadores                | 2                          |  |

| LEDs de usuario           | 8                          |  |

| Interruptores DIP         | 4                          |  |

La alimentación mediante el USB es muy práctica, aunque no siempre se puede tener acceso a una conexión de este tipo, la conexión externa es útil ya que con ella se puede incorporar la batería para el funcionamiento de la tarjeta.

#### 2.8. LUT

Una LUT, por sus siglas en ingles *Look Up Table*, es una tabla de consulta la cual contiene información en forma de vector, la cual ayuda para ahorrar tiempo de procesamiento ya que es más fácil obtener un valor previamente guardado que computarlo, aunque cuenta con la desventaja del costo de almacenamiento.

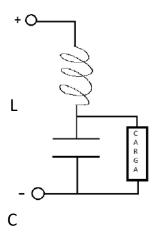

#### 2.9. Filtro LC

En los inversores, debido al proceso de modulación, la salida de la forma de onda no es senoidal, de hecho presenta una señal cuadrada (en términos generales) la cual inherentemente tiene un alto contenido armónico.

La función principal del filtro de salida consiste en disminuir los armónicos de alto orden sin afectar la frecuencia fundamental. Como en la modulación SPWM los anchos de pulso están en función de la amplitud de la senoidal, una vez que son filtradas la salida es senoidal (componente fundamental).

El circuito utilizado como filtro será un LC en paralelo el cual ha sido presentado en varios trabajos por su sencillez y operatividad, evidentemente este podría ser sustituido por uno de mayores prestaciones sin afectar o cambiar los otros componentes del inversor. Los elementos usados en el filtro limitan la potencia que estará a la salida, es decir la potencia que puedan soportar, considerando que los MOSFET soportan una mayor potencia. La respuesta a la frecuencia del filtro también definirá la ganancia en amplitud de la señal de salida.

El diagrama de conexión de un circuito LC en paralelo se presenta en la figura 10 donde L es el inductor y C el capacitor, en la figura se puede ver que el inductor se conectará a la parte positiva de la señal que se desea filtrar y el capacitor se conecta sobre la parte negativa. Para poder conectar la carga se deberá conectar el positivo en el nodo que comparten el inductor y el capacitor y el negativo ira directamente a la tierra del voltaje.

Figura 11 Diagrama de un filtro LC con carga donde "L" es el inductor y "C" el capacitor.

Los componentes seleccionados para el filtro influirán de manera significativa en la potencia suministrada por el inversor.

#### 2.10. Matlab

MATLAB combina un entorno de escritorio perfeccionado para el análisis iterativo y los procesos de diseño con un lenguaje de programación que expresa las matemáticas de matrices y arrays directamente.

#### 2.10.1. Simulink

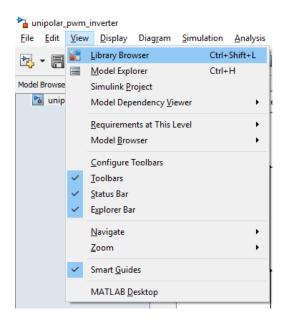

Es una herramienta para la simulación de sistemas, que permite tener un mejor resultado para llegar del concepto al código. Gracias a todas sus herramientas se puede simular el comportamiento de todas las partes del sistema.

Con Simulink se pueden reducir los prototipos caros mediante la realización de pruebas del sistema en condiciones que pueden ser riesgosas o lentas, además de que así se pueden validar el buen funcionamiento antes de llegar a lo físico.

Figura 12 Despliegue del menu para abrir Simulink.

Para abrir Simulink, en la ventana principal de Matlab en la pestaña de *new*, se da clic y en el listado se selecciona el apartado de "Simulink" en donde la primer opción es "Simulink model" al cual daremos clic, como se muestra en la figura 12.

Este abrirá una ventana nueva donde se muestra el área de trabajo. Para poder comenzar se deben definir los bloques que se usarán, los cuales se podrán agregar al espacio de trabajo mediante una nueva ventana de simulink; para abrir esta ventana, se clic en "View" para desplegar la pestaña y se da clic en la opción *Library Browser*, como se muestra en la figura 13.

Figura 13 Despliegue del menu para abrir Library Browser en Simulink.

En la nueva ventana de *Library Browser* se pueden encontrar todos los elementos necesarios para las simulaciones que se deseen realizar.

# Capítulo 3

Metodología

## 3. Metodología

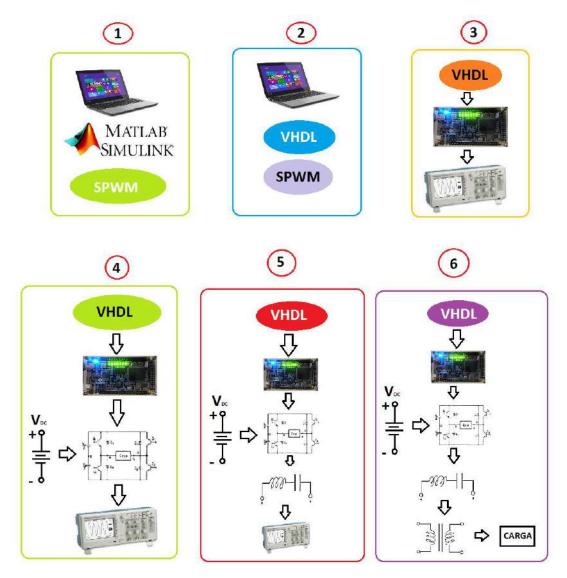

La metodología es dividida, como se muestra en la figura 14, en 6 pasos:

- El primer paso es realizar una simulación en Simulink de Matlab del SPWM para poder tener una referencia al momento de que se realice su descripción en VHDL. Con esta simulación se puede incluso ver cómo será la conexión del circuito con los MOSFET.

- 2) Al contar ya con una referencia de la modulación SPWM se hace la descripción en VHDL. Esta descripción dará como resultados los pulsos de activación para los MOSFET en el puente del inversor.

- 3) Es muy importante corroborar que los pulsos de activación funcionan correctamente, de tal modo que se probará en el FPGA el programa y con ayuda de un osciloscopio se verificaran los pulsos obtenidos en VHDL.

- 4) Ya que el FPGA mande los pulsos de manera correcta, se conecta el puente completo de MOSFET con el FPGA, el puente debe de tener en su entrada una fuente de DC para poder visualizar que está pasando de una señal DC a una de AC. Nota: En este paso aún no se verá una señal senoidal a la salida, aquí se verán los mismos pulsos que se obtuvieron en la simulación de Matlab del paso 1.

- 5) Para poder pasar de los pulsos cuadrados obtenidos en el paso 4 a una señal senoidal, la salida del inversor debe pasar por una etapa de filtrado, filtro LC. Se deben hacer diferentes pruebas con filtros a fin de obtener el que brinde una mejor salida.

- 6) Por último se harán pruebas de alimentación de cargas, estas cargas serán luminarias y motor eléctrico. Dependiendo de la fuente de alimentación del inversor y de la aplicación que se desee dar, se puede utilizar un transformador para poder incrementar el voltaje.

Figura 14 Metodología.

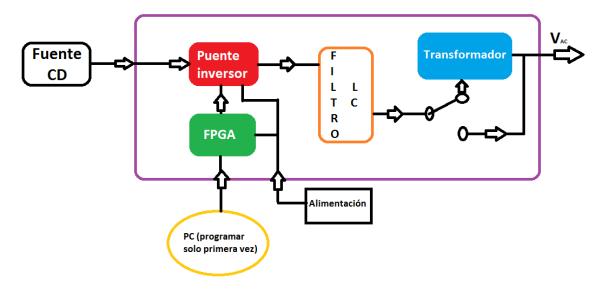

En la figura 15 se aprecia el diagrama general del inversor que se desarrollará. Como se puede observar tenemos una entrada de voltaje en CD y una salida de voltaje en AC. Lleva la programación del FPGA por medio de una PC, esto es para poder iniciar el inversor. La fuente de alimentación es para alimentar el FPGA y los componentes del puente inversor. También se aprecia la parte del filtro del inversor.

A la salida se puede ver un interruptor para definir si se ocupara la salida directamente o si se utilizará un transformador para poder subir el voltaje o bajarlo.

Figura 15 Diagrama general del Inversor.

# 3.1. Matriz de Experimentos

Para poder probar el inversor se definen los siguientes experimentos que son mostrados en la tabla 2

Tabla 2. Matriz de experimentos

| Fuente       | No° de prueba | Descripción                    |  |

|--------------|---------------|--------------------------------|--|

|              | 1             | Alimentación de un foco        |  |

|              |               | incandescente a 40 V, 60 V     |  |

|              |               | y 80 V, a 30 Hz, 60 Hz y 90    |  |

|              |               | Hz cada nivel de voltaje.      |  |

|              | 2             | Alimentación de un foco LED    |  |

| Fuente de CD |               | a 72 V y 80 V, a 50 Hz y 60    |  |

|              |               | Hz cada nivel de voltaje.      |  |

|              | 3             | Alimentación de una fuente     |  |

|              |               | de PC a 70 V y 80 V, a 50      |  |

|              |               | Hz y 60 Hz cada nivel de       |  |

|              |               | voltaje.                       |  |

|              | 4             | Alimentación de un motor       |  |

|              |               | eléctrico a 45 V, 60 V y 80 V, |  |

|              |               | a 30 Hz, 60 Hz y 90 Hz cada    |  |

|              |               | nivel de voltaje.              |  |

Como se puede apreciar en la Tabla 2 se harán pruebas con un máximo de 80V, esto debido a la fuente de CD que se tiene como entrada al inversor. En la prueba número 1 con el foco incandescente se harán pruebas con 3 valores de voltaje y frecuencia diferentes, esto se puede hacer debido al tipo de carga que es, al cambiar estos valores no le afecta en su funcionamiento, pero si tendremos un resultado diferente en cada uno de ellos. En las pruebas 2 y 3 se tiene menos flexibilidad para poder cambiar estos valores debido a que ambas cargas actúan por conmutación no se puede bajar tanto el voltaje de

entrada, si es menor no conmutaría y por ende no encendería y de cierta forma en cuanto se dé la conmutación el resultado será similar aun cuando se incremente el voltaje. En el caso de la frecuencia tampoco se tiene mucho margen de trabajo, se está limitado por los componentes electrónicos propios de las cargas, si se les somete a una frecuencia diferente dejarían de funcionar correctamente. Por último, en el caso número 4 se tiene una flexibilidad parecida a la del caso número 1, siendo aquí muy notorio cuando se cambie la frecuencia ya que la velocidad del motor se verá afectada.

El objetivo de probar el inversor con diferentes niveles de voltaje e de entrada es poder emular el comportamiento del inversor bajo distintas fuentes de voltaje, ejemplo: voltajes provenientes de paneles fotovoltaicos, baterías, aerogeneradores, u otras.

### 3.2. Simulación en Matlab

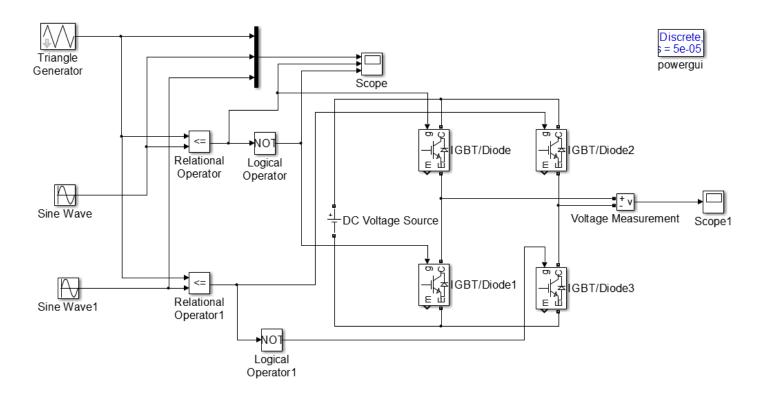

El primer paso dado fue la simulación en Matlab, mediante la cual se entiende de manera general los resultados que se deben obtener al realizar la síntesis de las señales en VHDL.

La herramienta de Matlab utilizada para esta simulación es simulink, en el cual se genera un diagrama a bloques a fin de obtener el modelo.

Los elementos utilizados en simulink son los mismos que serán utilizados en la práctica, a excepción de los IGBTs o MOSFET, siendo ellos los siguientes:

- Generador de señal triangular

- Generador señal senoidal (Φ = 0°)

- Generador señal senoidal (Φ = 180°)

- Comparadores

- Compuerta lógica NOT

- Puente completo de IGBT con diodos

La conexión de este diagrama se aprecia en la figura 16.

Las señales senoidales son comparadas con la triangular, teniendo así el modo de activación de los IGBT siendo que para una rama la señal de activación de un IGBT pasa a ser el complemento de la señal de activación del otro, esto a fin de no presentar cortocircuito en la rama.

La señal de salida del inversor se mide entre los nodos de salida y se suman, siendo uno considerado como positivo y el otro como negativo.

Figura 16 Diagrama a bloques en Simulink del inversor monofásico de puente completo con modulación SPWM.

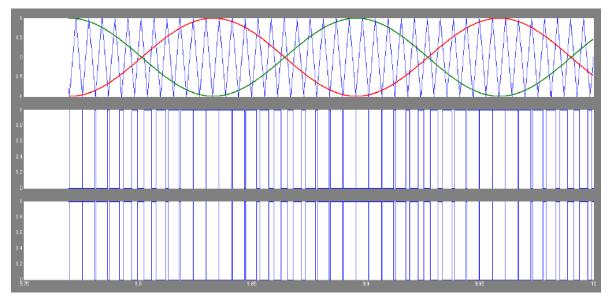

En la figura 17 se puede apreciar cómo es que se genera la modulación SPWM. En la primer "pantalla" del osciloscopio se puede apreciar las señales tanto senoidales como la triangular, en la segunda "pantalla" se muestra la salida correspondiente a la comparación de la señal senoidal con fase igual a cero, y en la tercer "pantalla" se puede ver la respuesta tras comparar la senoidal con fase igual a 180° con la señal triangular.

Figura 17 Modulación SPWM en Simulink.

La respuesta a la salida del puente se puede apreciar en la figura 18 donde se ve claramente el comportamiento de un inversor unipolar, un periodo de la señal tiene su semiciclo positivo y su semiciclo negativo; a esta salida se debe aplicar un filtro para poder obtener una señal de forma senoidal. Con esta parte se puede dar por terminada la primera parte, teniendo terminada la simulación del inversor en Simulink de Matlab.

Figura 18 Salida del inversor en Simulink sin filtrar.

### 3.3. SPWM en VHDL

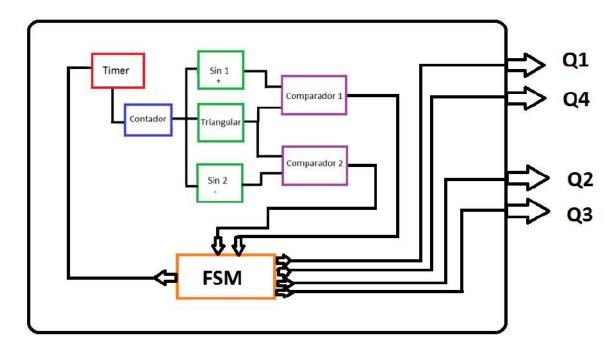

Para poder realizar la estructura digital del SPWM se utilizó el diagrama de la figura 19 donde se puede ver que los bloques necesarios son:

- LUTs (Senoidales y triangular)

- Comparadores

- Contador

- Timer

- FSM

Figura 19 Diagrama a bloques de la estructura digital del SPWM.

Tomando como referencia el diagrama a bloques de la figura 19 se ve que a partir de la máquina de estados se obtiene el pulso que da inicio a la cuenta del Timer, mismo que está diseñado para que cumpla con el tiempo necesario para poder ir llamando a cada uno de los valores de las LUTs, ya que cada pulso del Timer será un incremento en el contador que es la entrada de las LUT. A fin de poder utilizar un solo contador y un solo Timer, las LUT tienen el mismo número de muestras asegurando que siempre para cada valor de la señal senoidal se tendrá un valor para comparar de la señal triangular. Posteriormente se tienen dos módulos de comparación, en el primer módulo deberá entrar la señal triangular y la señal senoidal de fase igual a 0° y en el segundo módulo la misma

señal triangular pero con la señal senoidal de fase igual a 180°. El comparador entregará como resultado un pulso cuando la señal triangular sea mayor que la senoidal en ambos casos. Esta señal deberá entrar a la máquina de estados en la cual se tienen contemplados los tiempos de retardo de activación y desactivación de los MOSFET, estos tiempos como ya se mencionó son de gran importancia debido a que sin ellos se podría presentar una condición de cortocircuito y dañar los tiristores; siendo así las salidas de la máquina de estados los pulsos Q1, Q2, Q3 y Q4 correspondientes para los MOSFET. Es importante recordar que las señales están asignadas de acuerdo a la figura 5 donde se tiene un puente completo, de tal manera que Q1 y Q4 van a ser señales complementarias así como lo son Q2 y Q3 de igual forma.

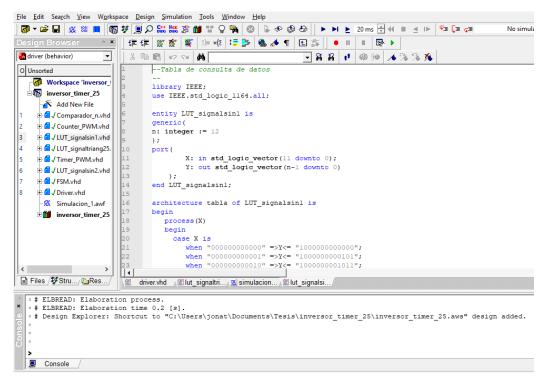

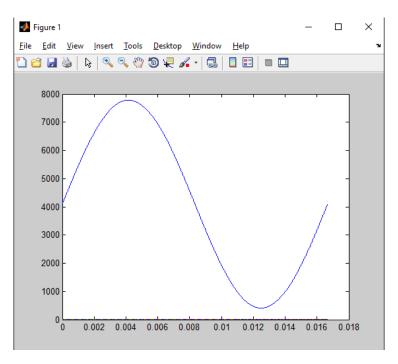

## 3.4. Generación de las LUT con Matlab

A fin de poder obtener una mejor calidad en la señal se utilizó Matlab para generar una GUI y así la señal con amplitud y frecuencia deseadas. Ya que se tiene la señal esta es muestreada y guardada en un vector en cual con ayuda del comando "fopen" se puede vaciar en un archivo. Este archivo se puede generar con la estructura de un archivo en VHD que sin ningún problema puede ser utilizado de forma directa, debido a que la forma de la descripción del vaciado está escrita a conveniencia.

Cabe señalar que para los fines de las señales no es necesario cumplir con parámetros muy específicos, más que cuidar la amplitud, ya que de ellas depende el índice de modulación; la frecuencia de muestro se acopla de tal manera que el número de muestras de las 3 señales sea el mismo, asegurando que para cada valor de la señal triangular exista un valor para comparar con las señales senoidales.

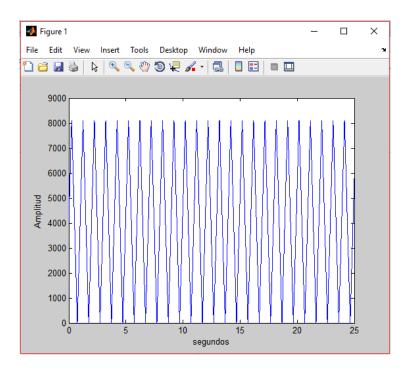

En la figura 20 se tiene una señal triangular, la cual será la señal portadora, que en este caso es de 25 periodos, si se desea hacer de más no habría ningún problema, pues al momento del muestreo se obtendrá un número finito de valores a fin de poder comparar con las señales senoidales.

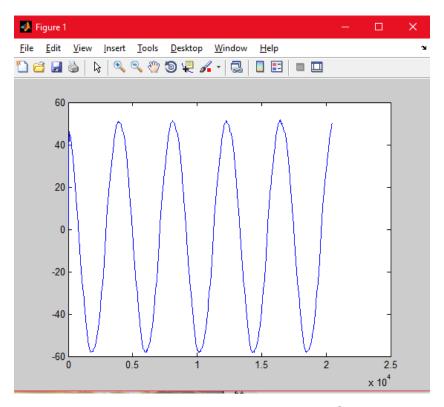

Figura 20 Señal triangular a muestrear.

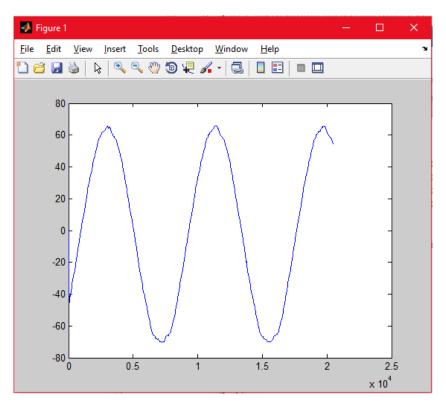

La señal que se muestra en la figura 21 es la senoidal con fase de 0° que será muestreada, al igual que con la señal triangular se muestreara para obtener un número finito de valores.

Si se realiza una comparación de los ejes de tiempo (eje x) de las figuras 20 y 21 será notorio que no coinciden, pero esto no afecta al sistema dado que al momento de realizar el muestreo los vectores de cada una de las señales la magnitud será igual, dejando sin importancia el eje x de la gráfica.

Figura 21 Señal senoidal a muestrear con fase de 0°.

Para poder trabajar las LUT se necesita de un contador que mande llamar a cada elemento del arreglo, esto debido a que como fue guardado en un vector se tiene que llamar a la posición del vector deseada. Esto se cumple para las 3 LUT con las que se está trabajando.

Para que el inversor funcione de la manera deseada el contador debe aumentar la cuenta cada un tiempo determinado, esto se logra por medio del timer. El timer trabaja con el clock del FPGA el cual en este caso es de 50 MHz, y manda un pulso cada que se cumple cierto número de pulsos generados por el clock, este pulso será el que recibirá el contador y podrá aumentar la cuenta. De este modo el sistema podrá ofrecer una salida de 60 Hz que es lo que se necesita a la salida.

Debido a que las 3 LUT presentan el mismo número de muestras bastará con un solo timer y un solo contador. A partir de las salidas generadas por las LUT, estas deberán ser evaluadas en los módulos de comparación y así poder obtener los pulsos de accionamiento de los tiristores

Para la parte de comparación se tienen 2 partes:

Comparación de la señal triangular con la señal senoidal con fase igual a 0°

### 2) Comparación de la señal triangular con la señal senoidal con fase igual a 180°

A la salida de los comparadores se obtendrá una salida de cada uno ellos, del primer comparador se dará una señal en alto cuando la señal triangular sea mayor que la senoidal con fase de 0°, y en el segundo comparador lo hará cuando la triangular sea mayor que la senoidal con fase de 180°. Estas señales deberán entrar a la máquina de estados, de la cual se obtendrán las 4 salidas de activación para los MOSFET. Estas salidas deben de incluir ya un pequeño tiempo muerto, esto debido a que en los tiristores reales se presenta un tiempo de encendido y un tiempo de apagado, si no se tiene la debida precaución con estos tiempos el sistema podría entrar en un estado de cortocircuito lo cual ocasionaría que los MOSFET se dañaran, dando como resultado un mal funcionamiento del inversor. Este tiempo de retardo es de 1 us, este tiempo sobrepasa los tiempos estimados en las datasheet de los componentes, deja el tiempo suficiente para la correcta activación y desactivación de los componentes y sigue siendo lo suficientemente pequeño para no afectar al correcto funcionamiento del inversor.

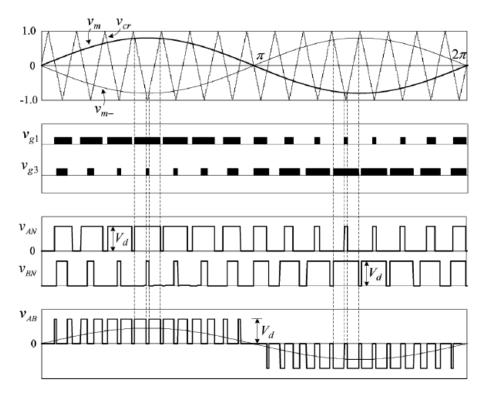

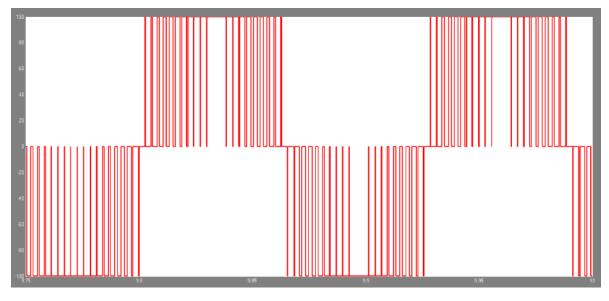

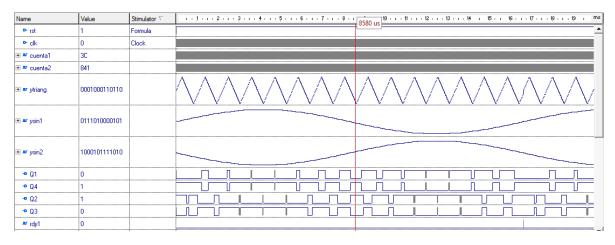

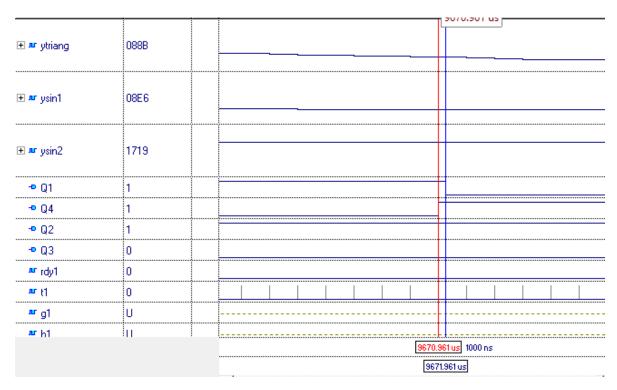

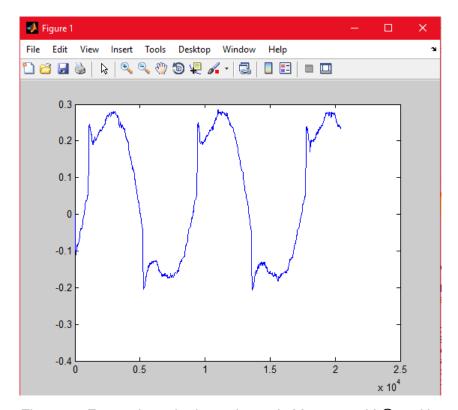

El resultado de la simulación de la descripción en VHDL es el que se muestra en la figura 22, donde se pueden apreciar las 3 salidas de las LUT y las salidas Q1, Q2, Q3 y Q4.

Figura 22 Simulación del programa de modulación SPWM.

Un detalle muy importante es que los tiempos de retardo son dados con la máquina de estados, considerando la activación y desactivación únicamente de los switch involucrados de la misma rama, esto con el fin de no hacer desactivaciones innecesarias. Los tiempos de retardo realmente son muy pequeños por lo cual no presentan ninguna clase de afectación a la salida. Se pueden apreciar los tiempos de retardo en la figura 23.

Figura 23 Tiempo de desactivación mostrado para los switch Q1 y Q4.

## 3.5. Prueba del programa en FPGA

Tras la elaboración de la estructura digital el siguiente paso es cargar el programa a un FPGA. Esto se realizará en dos pasos 1) verificar que la salida de los pulsos sea la correcta, esto debido a que en algunas ocasiones la simulación parece estar correcta y hay errores que no son visibles en esta pero si en la implementación; 2) habiendo verificado los pulsos de activación de los MOSFET que salen del FPGA, conectar al puente completo de MOSFET y ver su salida.

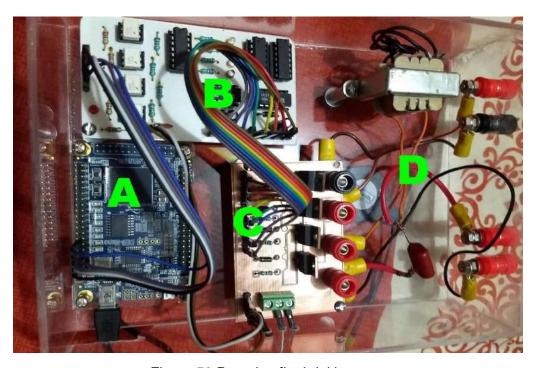

La tarjeta utilizada es una ALTERA Cyclone IV DE0-nano EP4CE22F17C6N como la que se muestra en la figura 24, esta tarjeta es utilizada ya que tiene una alta velocidad de procesamiento (50 MHz) la cual es suficiente para trabajar con los MOSFET además nos da la versatilidad de posibles trabajos de investigación a futuro.

Figura 24 Tarjeta ALTERA DE0- Nano Cyclone IV EP4CE22F17C6N.

## 3.5.1. Síntesis del programa

La plataforma de altera proporciona su sintetizador que es llamado Quartus. Este sintetizador sirve para poder implementar las descripciones hechas en VHDL en una tarjeta FPGA de Altera.

Cuando se crea un nuevo proyecto en Quartus se puede hacer la descripción aquí mismo o importar los archivos que ya sean existentes. Después de probar que el programa no tiene errores al sintetizar, se deberá hacer la asignación de los pines de la tarjeta que se van a utilizar para poder mandar los pulsos al puente de los MOSFET. Posterior a esto se va a generar un archivo el cual será el que se programara en la tarjeta.

Dentro del mismo sintetizador se tiene un programador, en el cual solo pide agregar el archivo de programación y con un click se cargara el programa indicando en la interfaz del programador si se ha cargado con éxito el programa.

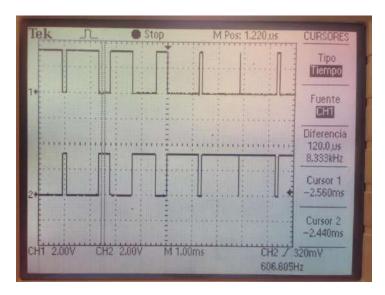

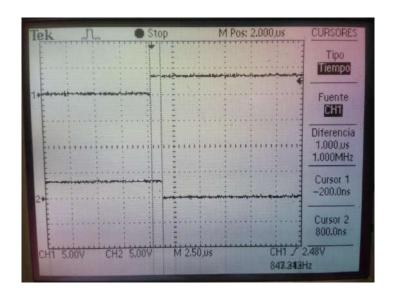

## 3.5.2. Visualización de los pulsos en el osciloscopio

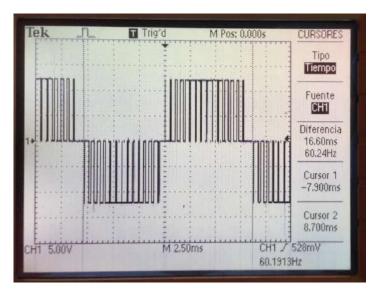

Una vez que se ha cargado el programa en la FPGA se pueden ver los pulsos correspondientes para la activación de los MOSFET en los pines de salida. Es necesario recordar que estos pulsos deben ser los correctos porque de no ser así se pueden generar cortocircuitos en el puente.

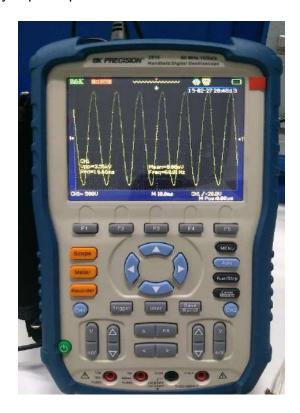

Figura 25 Respuesta de la modulación SPWM para Q1 y Q4.

Para poder visualizar los pulsos se hace uso de un osciloscopio, el cual tiene una pequeña limitante al tener solo dos canales, de tal forma que solo se podían ver dos señales al mismo tiempo. Las señales que se aprecian en la figura 25 son las correspondientes a las señales Q1 y Q4, las cuales como se puede ver en la imagen son complementarias. En la figura 26 se muestra el retraso que existe entre estas mismas señales, que como se ha mencionado con anterioridad juegan un papel muy importante en la implementación.

Figura 26 Visualización del tiempo de retardo presente entre las señales Q1 y Q4.

### 3.5.3. Puente de MOSFET

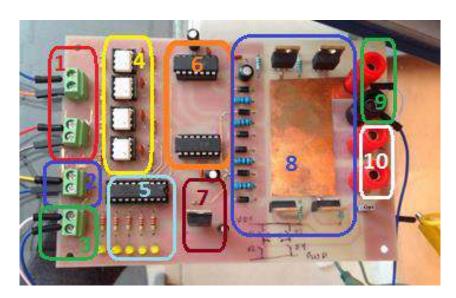

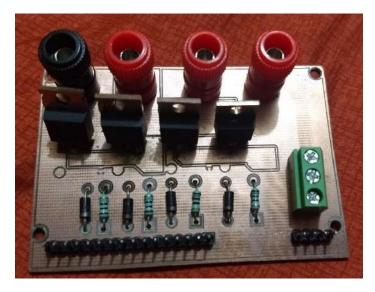

El diseño que se utilizó para estas primeras pruebas es mostrado en la figura 27. A continuación se describen las etapas que presenta este diseño.

Figura 27 Prototipo de tarjeta para inversor

- 1. Entrada de las señales del FPGA (Q1, Q2, Q3 y Q4 respectivamente de arriba hacia abajo).

- 2. Entrada de la tierra digital, proviene del FPGA.

- Como todo voltaje se debe referenciar con su respectiva tierra. Esta tierra solo entra en la parte del optoacoplamiento.

- 3. Alimentación de 12  $V_{CD}$ .

- Esta es la alimentación necesaria para los componentes que se encuentran en la tarjeta.

- 4. Aislamiento de la parte digital con la parte analógica por medio de optoacopladores. Es muy importante tener este aislamiento de la parte digital con el resto del circuito, el optoacoplador es muy útil para esto, ya que la función que tiene es por medio de un diodo LED que al emitir luz satura un fototransistor, dando así paso al voltaje a la entrada del optoacoplador.

- 5. Buffer para visualización del correcto funcionamiento del optoacoplamiento.

Esta parte solo permite saber si la etapa de optoacoplamiento se está llevando bien acabo. El buffer es utilizado únicamente con el propósito de no afectar al voltaje que va a ir a los drivers.

6. Drivers para accionamiento de los MOSFET.

Por lo regular es necesario tener un driver que no de la señal de accionamiento de los MOSFET, más en cuanto a aplicaciones de potencia se refiere.

7. Regulador de voltaje a 12  $V_{CD}$ .

El regulador de voltaje nos ayuda a mantener un voltaje constante para los elementos que se encuentran en la tarjeta, esto evita que se generen cambios en las señales de activación.

8. Puente de MOSFET con su circuito de disparo.

Cada MOSFET tiene su propio circuito de disparo así como de un diodo para evitar las corrientes de retorno.

9. Entrada de la fuente de CD al inversor.

Aquí es donde se introducirá el voltaje en CD que se desea convertir en CA. Dicho voltaje puede provenir de diferentes fuentes (panel fotovoltaico, aerogenerador, batería).

10. Salidas del inversor (A y B respectivamente de arriba hacia abajo).

La lectura de la salida del inversor se realiza en estos nodos.

## 3.5.4. Implementación del FPGA con el puente de MOSFET

Al tomar la lectura en AB se observa la forma de onda de la figura 28. Hay que destacar que esta señal es la se esperaba ver de acuerdo a la simulación hecha en Matlab de la figura 18.

La señal de salida no se parece aun a una señal senoidal, si tiene su semiciclo positivo y su semiciclo negativo, por lo cual esta señal debe de pasar por una etapa de filtrado a fin de obtener la señal senoidal.

Figura 28 Salida del inversor medida en AB.

## 3.6. Etapa de filtrado (filtro LC)

El filtro que se utiliza es un filtro de segundo orden LC, con este filtro se atenúan las armónicas presentes de alto orden lo cual mejorará el parámetro THD.

Recordando que la frecuencia de corte de un filtro LC es de

$$f_C = \frac{1}{2\pi\sqrt{LC}} \tag{8}$$

Las pruebas de filtrado se realizaron a diferentes niveles de tensión a fin de poder ver su desempeño en diferentes situaciones.

Es importante mencionar que se decide hacer estas pruebas de forma experimental con el objetivo de hacer un análisis de resultados de forma práctica/empírica.

## 3.6.1. Filtro 1

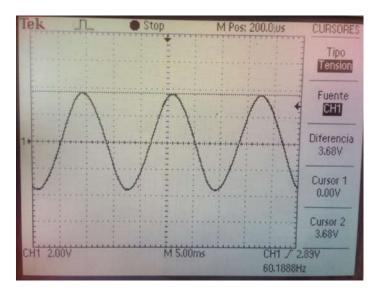

Para las pruebas preliminares se utilizó un pequeño filtro de baja potencia. El valor del capacitor para este filtro es de 0.47uF y como inductor se utilizó un pequeño transformador de baja potencia.

### 3.6.1.1. Pruebas a diferentes niveles de tensión

El pequeño filtro se utilizó simplemente para ver la respuesta de la salida ante un filtro.

La primera prueba fue a 12V, el filtro entrega una señal senoidal pero presenta el detalle de la eficiencia, siendo esta muy baja pues a la salida solo nos entregaba  $3.68V_{pico}$  como se puede observar en la figura 29. Evidentemente estos resultados tienen que ver con la respuesta a la frecuencia o BODE del filtro.

Figura 29 Respuesta con el filtro 1 (C=0.47uF) con una entrada de 12V.

Segunda prueba: 20V. Como se dio a notar en la primera prueba el filtro tiene una gran pérdida, esto se debe a la atenuación de la señal debido a su frecuencia de corte. Para el caso en que se tiene una entrada de 20V la salida del inversor es de 5.92V (Figura 30).

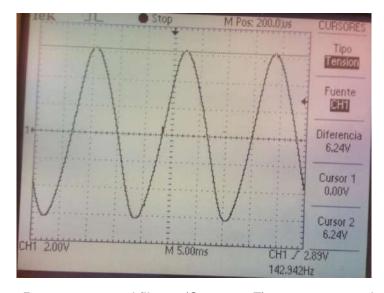

Tercer prueba: 30V. Es de esperarse obtener un bajo voltaje a la salida del inversor, se obtuvieron 6.24V, como se ve en la figura 31.

Con estas pruebas se observan los siguientes aspectos:

- 1) El filtro LC cumple con la labor de otorgar una señal senoidal.

- 2) A medida que se va aumentando el voltaje la eficiencia disminuye (inherente al BODE y comportamiento de los componentes individuales del filtro).

Figura 30 Respuesta con el filtro 1 (C = 0.47uF) para una entrada de 20V.

Figura 31 Respuesta con el filtro 1 (C = 0.47uF) para una entrada de 30V.

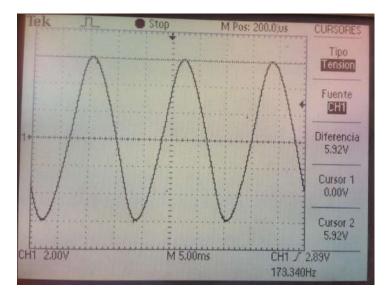

## 3.6.2. Filtro 2

Para este filtro se utilizó un inductor de 2mH y un capacitor de 20uF, de tal forma que la frecuencia de corte es de

$$f_C = 795 \, Hz \tag{9}$$

### 3.6.2.1. Pruebas a diferentes niveles de tensión

Con este segundo filtro se manejaron los mismos niveles de tensión que con el primer filtro para poder comparar su rendimiento.

## 1) Prueba a 12V

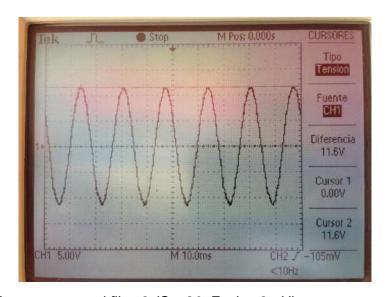

Para la primer prueba se introdujeron 12V al inversor y a la salida se obtuvo un valor que mejoró considerablemente en comparación con el resultado del primer filtro. En la figura 32 se puede apreciar la salida del inversor.

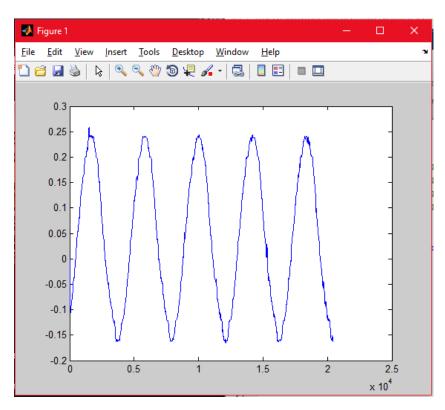

Figura 32 Respuesta con el filtro 2 (C = 20uFyL = 2mH) para una entrada de 12V.

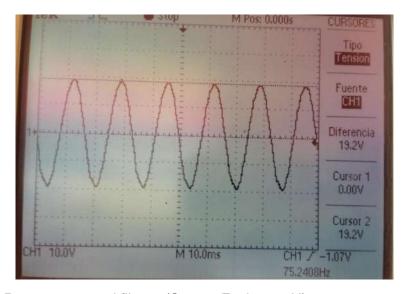

Figura 33 Respuesta con el filtro 2 (C = 20uFyL = 2mH) para una entrada de 20V.

## 2) Prueba a 20V

Al igual que en la prueba anterior, el inversor presenta pérdidas cuando se sube el voltaje de entrada. Pero en este caso no hubo tanta pérdida como en el caso anterior (Ver figura 33).

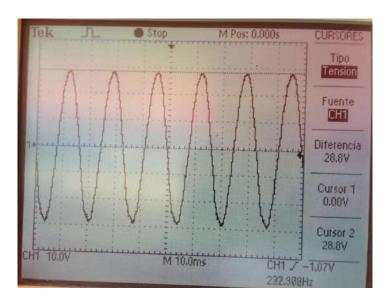

## 3) Prueba a 30V

En esta última prueba se puede ver cómo es que el que el inversor tiene pérdidas muy bajas en comparación con el caso del filtro anterior. Para el voltaje de entrada de 30V en CD entrega un voltaje de salida de 28.8 en CA, esto se puede apreciar en la figura 24.

Figura 34 Respuesta con el filtro 2 (C = 20uF y L = 2mH) para una entrada de 30V.

De estos resultados y análisis se obtienen los parámetros a usar en el filtro, cabe mencionar que también se han ajustado a los valores que se tienen disponibles al momento de la realización de este proyecto.

# Capítulo 4

Experimentación y Resultados

## 4. Experimentación y resultados

A continuación se presentan los experimentos y los resultados obtenidos para la matriz de pruebas presentada en la sección anterior.

## 4.1. Alimentación de cargas

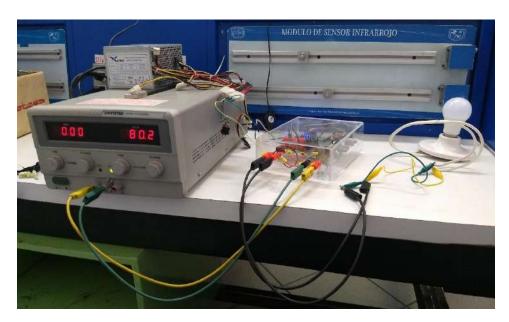

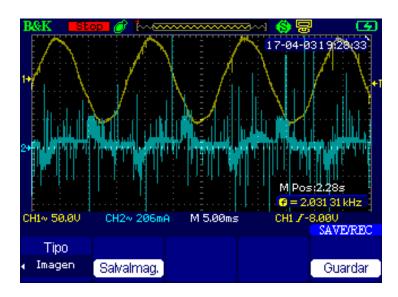

Ahora que ya se tiene las salidas del inversor verificadas, es posible alimentar cargas con él. Es muy importante recordar que los niveles de tensión que se tienen normalmente en las diversas fuentes de CD son de entre 12V y 36V, por lo cual se necesita de una etapa de transformación a fin de poder suministrar el nivel de voltaje necesario para las cargas.

Un punto que se debe destacar es que se desarrolló un inversor genérico, de tal forma las pruebas se realizaron a un alto nivel de tensión para comprobar que el inversor puede trabajar a diferentes niveles de tensión, no solo bajos, sino también con altos.

## 4.1.1. Fuente de alto voltaje

Dentro del laboratorio de la facultad de ingeniería se tiene una fuente de aproximadamente 110V de corriente directa, la cual es de gran utilidad para las pruebas que se realizarán de acuerdo a la matriz de experimentos.

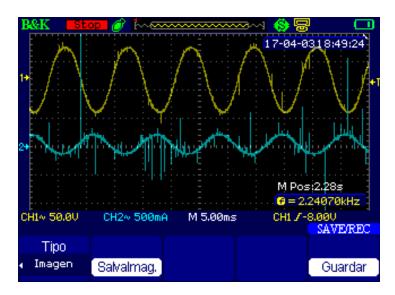

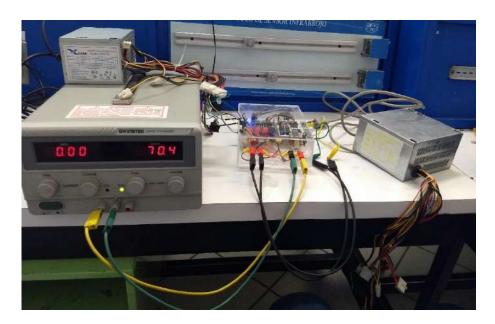

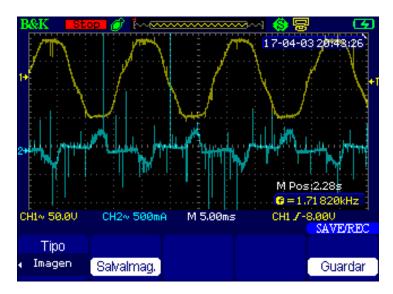

## 4.1.2. Alimentación de Luminaria Incandescente

En esta prueba se alimentó un foco incandescente convencional de 40W a diferentes niveles de tensión de entrada (40 V, 60 V y 80 V) y a diferentes niveles de frecuencia (30 Hz, 60 Hz y 90Hz).

Figura 35 Interconexión para prueba con foco incandescente..